现在VGA的技术在电脑显示器方面应用广泛,这是在87年提出的视频传输标准,其优点非常突出并且能够应用在电脑、笔记本等设备,但对于拥有高分辨率图像的电脑却很少用到。但大家可能对VGA的显示原理可能有些不清楚,那么下面小编就对嵌入式VGA显示的实现方法对大家进行一番讲解。

一、显示原理与VGA时序实现

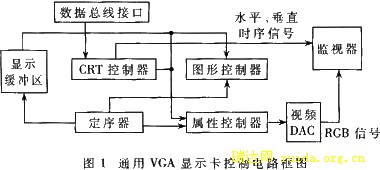

如图大家可以看见控制电路、显示缓存区和视频BIOS程序三个部分组成了通用VGA显示卡系统。而在控制电路主要完成时序发生、显示缓冲区数据操作、主时钟选择和 D/A转换等功能;显示缓冲区提供显示数据缓存空间;视频BIOS作为控制程序固化在显示卡的 ROM中。

二、VGA时序分析

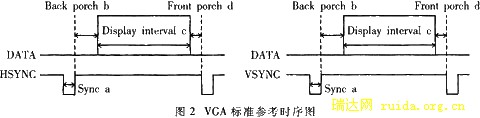

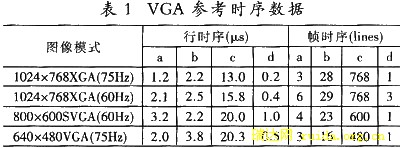

那么经过上面讲解后,大家对VGA显示卡工作原理应该有一定的了解了,要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。VGA的标准参考显示时序如图2所示。行时序和帧时序都需要产生同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四个部分。几种常用模式的时序参数如表1所示。

三、 数据宽度和格式

为了节省显存的存储空间,可采用高彩色图像,即每个像素值由16位表示,R、G、B三个分量分别使用5位、6位、5位,比真彩色图像数据量减少一半,同时又能满足显示效果。如果VGA显示真彩色BMP图像,则需要R、G、B三个分量各8位,即24位表示一个像素值,很多情况下还采用32位表示一个像素值。

四、读SRAM地址的产生方法

由于采用两片SRAM,所以最高位地址作为SRAM的片选使用。由于信号经过CPLD内部逻辑器件时存在一定的时间延迟,在CPLD产生地址和读信号读取数据时,读信号、地址信号和数据信号不能满足SRAM读数据的时序要求。可以利用硬件电路对读信号进行一定的时序调整,使各信号之间能够满足读SRAM和为DAC输入数据的时序要求。主时钟作为像素点计数脉冲信号,同时提供显存SRAM的读信号和D/A转换时钟,它所驱动的计数器的输出端作为读SRAM的低位地址。行同步信号作为行数计数脉冲信号,它所驱动的计数器的输出端作为读SRAM的高位地址。

五、VGA时序实现

首先,在CPLD中利用计数器和RS触发器,以计算出的各时序段时钟周期数为基准,产生不同宽度和周期的脉冲信号,再利用它们的逻辑组合构成图2中的a、b、c、d各时序段以及D/A转换器的空白信号BLANK和同步信号SYNC。根据刷新频率确定主时钟频率,然后由主时钟频率和图像分辨率计算出行总周期数,再把表1中给出的a、b、c、d各时序段的时间按照主计数脉冲源频率折算成时钟周期数。

需要技术服务: 李师傅电话18277394428