简介:德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motor control, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C 语言的环境中搭配汇编语言来撰写程序。值得一提的是,F28x DSP 核心支持特殊的IQ-math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。F28x 系列DSP预计发展至400MHz,目前已发展至150MHz 的Flash 型式。

1.高性能静态CMOS制成技术

(1)150MHz(6.67ns周期时间)

(2)省电设计(1.8VCore,3.3VI/O)

(3)3.3V快取可程序电压

2.JTAG扫描支持

3.高效能32BitCPU

(1)16x16和32x32MAC Operations

(2)16x16Dual MAC

(3)哈佛总线结构

(4)快速中断响应

(5)4M线性程序寻址空间(LinearProgramAddressReach)

(6)4M线性数据寻址空间(LinearDataAddressReach)

(7)TMS320F24X/LF240X程序核心兼容

4.芯片上(On-Chip)的内存

(1)128Kx16 Flash(4个8Kx16,6个16Kx16)

(2)1Kx16OTPROM(单次可程序只读存储器)

(3)L0和L1:2组4Kx16 SARAM

(4)H0:1组8Kx16SARAM

(5)M0和M1:2组1Kx16 SARAM

共128Kx16 Flash,18Kx16 SARAM

5.外部内存接口

(1)支持1M的外部内存

(2)可程序的Wait States

(3)可程序的Read/Write StrobeTi最小g

(4)三个独立的芯片选择(Chip Selects)

6.频率与系统控制

(1)支持动态的相位锁定模块(PLL)比率变更

(2)On-Chip振荡器

(3)看门狗定时器模块

7.三个外部中断

?8.外围中断扩展方块(PIE),支持45个外围中断

9.128位保护密码

(1)保护Flash/ROM/OTP及L0/L1SARAM

(2)防止韧体逆向工程

10.三个32位CPU Timer

11.电动机控制外围

(1)两个事件管理模块(EVA,EVB)

(2)与240xADSP相容

12. (1)同步串行外围接口SPI模块

(2)两个异步串行通讯接口SCI模块,标准UART

(3)eCAN(Enhanced Controller Area Network)

(4)McBSP With SPI Mode

13.16个信道12位模拟-数字转换模块(ADC)

(1)2x8通道的输入多任务

(2)两个独立的取样-保持(Sample-and-Hold)电路

(3)可单一或同步转换

(4)快速的转换率:80ns/12.5MSPS

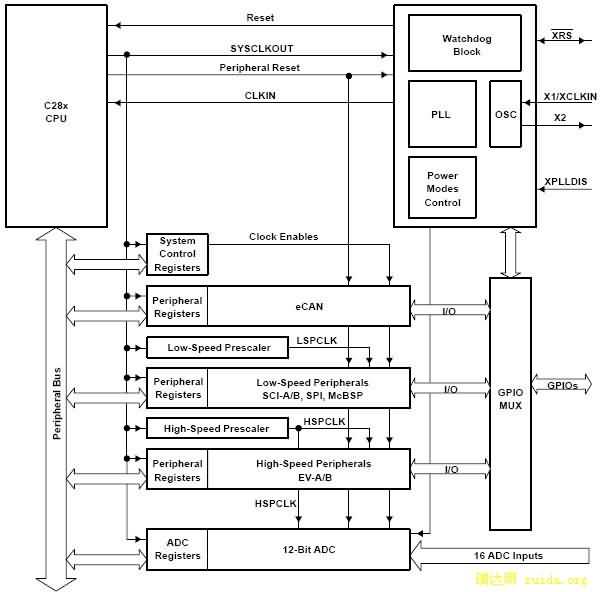

图1TMS320F2812功能方块图。

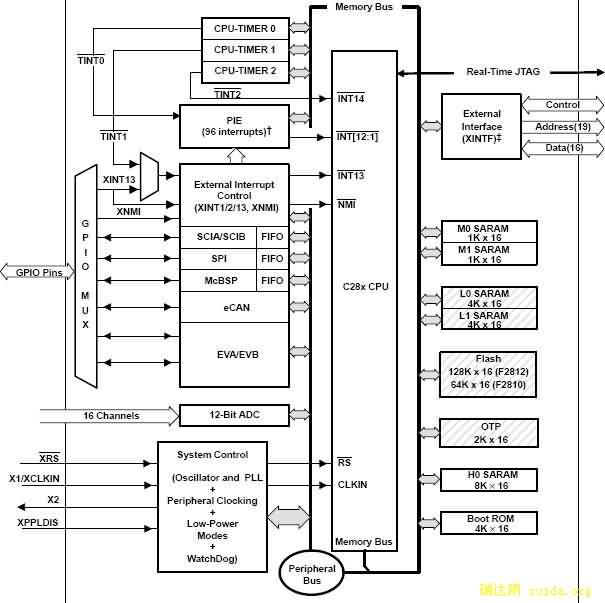

2.2TMS320F2812硬件结构介绍

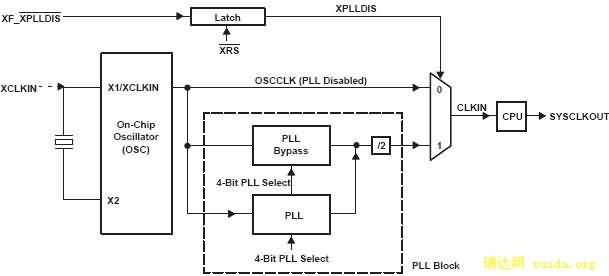

2.2.1OSC与PLL方块

F2812芯片上设计了一个相位锁定模块(PLL),这个模块将会提供整个芯片所需频率源。PLL模块方块图如图2所示。PLL提供了4 位(PLLCR[3:0])的PLL倍率选择,共10种放大倍率,可动态改变CPU的频率频率。如表1所示为PLLCR 缓存器的格式,缓存器的位说明如表2所示。

XCLKIN:外部频率源输入。

OSCCLK:与XCLKIN的频率一样。

CLKIN:CPU维持正常工作所需的频率源。这是整个芯片的最高频率。

SYSCLKOUT:与CLKIN的频率一样,提供给外围电路使用。

图2 OSC与PLL方块图。

表1PLLCR缓存器位格式表:

15-4 3 2 1 0 Reserved DIV R-0 R/W-0

R:读取;R/W:可读可写;-0=重置后的值

NOTE:EALLOW-protected register

表2 PLLCR缓存器位说明表:

位 名称

功能描述

15-4 Reserved 保留 3-0DIV DIV 可以控制(不论PLL是否在旁路状态皆可控制)及设定(仅在PLL 为非旁路状态时才可设定)PLL的频率比:=0000,CLKIN =OSCCLK/2(PLL bypass)

=0001,CLKIN =(OSCCLK*1.0)/2

=0010,CLKIN =(OSCCLK*2.0)/2

=0011,CLKIN =(OSCCLK*3.0)/2

=0100,CLKIN =(OSCCLK*4.0)/2

=0101,CLKIN =(OSCCLK*5.0)/2

=0110,CLKIN =(OSCCLK*6.0)/2

=0111,CLKIN =(OSCCLK*7.0)/2

=1000,CLKIN =(OSCCLK*8.0)/2

=1001,CLKIN =(OSCCLK*9.0)/2

=1010,CLKIN =(OSCCLK*10.0)/2

=1011-1111 ,保留

2.2.2系统频率控制

如图3所示,所有外围电路的频率都是由SYSCLKOUT经过除频而

来,F2812将所有外围分成两类,分别是:

1.高速外围:包括事件管理模块(EVA,EVB)及ADC。

2.低速外围:包括SCI-A/B、SPI、McBSP。

HSPCLK:高速外围的频率,可经由HISPCP缓存器改变其频率,如表

2-3所示为HISPCP缓存器的格式,缓存器的位说明如表4所示。

LSPCLK:低速外围的频率,可经由LOSPCP缓存器改变其频率,如表

2-5所示为LOSPCP缓存器的格式,缓存器的位说明如表6所示。

表3HISPCP缓存器位元格式表:

15-3 2 1 0 Reserved HSPCLK R-0 R/W-001

R:读取;R/W:可读可写;-0=重置后的值

NOTE:EALLOW-protected register

表4 HISPCP 缓存器位元说明表:

位元名称

功能描述

15-3 Reserved 保留 2-0HSPCLK这些位元设定高速外围频率比(HSPCLK)与SYSCLKOUT的关系:如果HISPCP≠0,HSPCLK=SYSCLKOUT/(HISPCPx2)

如果HISPCP=0,HSPCLK =SYSCLKOUT

=000,高速频率= SYSCLKOUT/1

=001,高速频率= SYSCLKOUT/2( 预设值)

=010,高速频率= SYSCLKOUT/4

=011 ,高速频率= SYSCLKOUT/6

=100,高速频率= SYSCLKOUT/8

=101,高速频率= SYSCLKOUT/10

=110 ,高速频率= SYSCLKOUT/12

=111 ,高速频率= SYSCLKOUT/14

表5 LOSPCP缓存器位元格式图:

15-3 2 1 0 Reserved LSPCLK R-0 R/W-010

图7 CPU-Timers 方块图

2.5事件管理模块(EVA,EVB)

如图8事件管理模块包括一般用途定时器(General-Purpose,GPTimers)、全比较(full-compare)/PWM 单元、补抓单元(capture)及四象限编码器(QEP)电路,如此丰富的功能足以用于动态控制(motion control)及电机控制(motor control)的应用。如表9所示,这两个事件管理模块(EVA和EVB)

有相同的外围,能够控制2个三相电动机,可以应用于多轴动态控制。

图8事件管理模块(EVA)之功能方块图。

表9事件管理模块和信号名称:

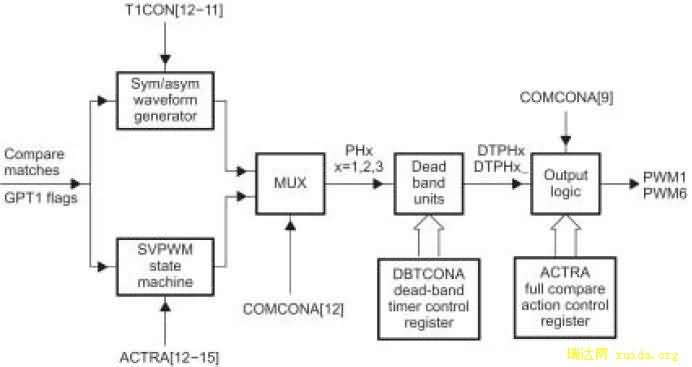

2.5.1脉波宽度调变(PWM)

PWM的功能包括:

1.拥有宽广可程序的Dead-time长度。

2.PWM载波频率实时的改变。

3.PWM脉波宽度实时的改变。

4.可以透过程序来产生非对称、对称及空间向量PWM信号。

5.提供外部保护接脚PDPINTx来保护功率级板,当这个接脚为”LOW”时,PWM信号将会强制变为高阻抗.如图9所示为PWM 电路的方块图,其动作流程大致为:比较器的值(CMPRx)进来与T1CON所设定的对称或非对称之波形比较,然后产生方波PHx输出进入Dead-time 产生电路产生出两个有

Dead-time的信号,再透过输出逻辑电路来设定每个PWM的输出逻辑,如此就可产生所需要的PWM信号。

图9 PWM 电路方块图

如图10 所示为非对称PWM 波形图,其中PWM1、PWM3、PWM5输出逻辑设为Active High,PWM2、PWM4、PWM6 输出逻辑设为ActiveLow,如此设定Dead-time 会使得PWMx 与PWMX+1 两讯号不同时为High,适用于IGBT 为Active High 之功率级板。

图10非对称PWM信号波形图(x=1,3,or5)。

如图11所示为对称PWM波形图,其中PWM1、PWM3、PWM5 输出逻辑设为ActiveLow,PWM2、PWM4、PWM6输出逻辑设为ActiveHigh,如此设定Dead-time会使得PWMx与PWMX+1两信号不同时为Low,适用于IGBT为ActiveLow之功率级板,本系统就是用这个设定方式。

图11对称PWM信号波形图(x=1,3,or5)。

2.5.2QEP单元

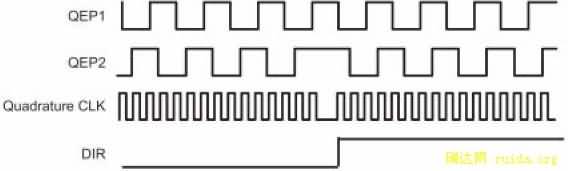

每个事件管理模块都有一个四象限编码计数电路(QEP电路),使用者可以藉由这个电路将光编码器两个相差90度的信号送到EVA 的CAP1/QEP1及CAP2/QEP2或EVB的CAP4/QEP3及CAP5/QEP4,来取得位置与速度的信息。F2812能够透过EVA和EVB 撷取两个Encoder的信号。EVA的QEP电路以GPtimer2为频率基础,而EVB的QEP电路以GPtimer4为频率基础,与F240 最大的差异在于无法合并两个16位的定时器来扩展成32位的定时器,只能以16位的定时器来使用。QEP 电路的定时器之计数模式必需操作于”方向性上数/下数计数模式”。EVA的QEP电路方块图如图12所示。EVB的QEP电路方块图如图13所示。

图12EVA的QEP电路方块图。

图13EVB的QEP电路方块图。

如图14所示为典型的Encoder输出信号,在图的左半部,看到QEP1领先QEP2为90 度,所以定时器使用上数型。在图的右半部,看到QEP2领先QEP1为90度,所以定时器使用下数型。

图14QEP的解碼时序及方向图。

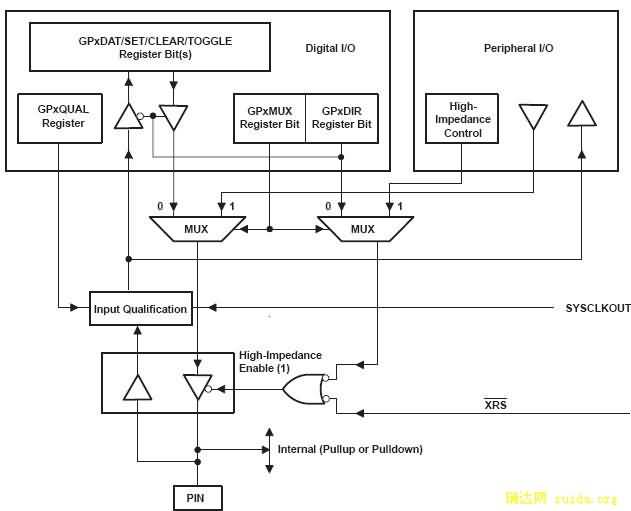

2.6通用输入/输出(GPIO)接口

图15为GPIO的方块图,F2812许多外围都与GPIO共享接脚,使用时需要设定GPxMUX、GPxDIR、GPxQUAL、GPxDAT 等缓存器来达到硬件上的运用。

GPxMUX:每个I/O端口都有一个多任务缓存器(GPxMUX),GPxMUX 缓存器是用来选择这些接脚被拿来当做数字I/O(GPxMUX.bit=0)还是外围I/O(GPxMUX.bit=1)。当DSP重置时,所有I/O 预设为数位I/O。

GPxDIR:每个I/O端口都有一个方向控制缓存器(GPxDIR),用来设定为数字I/O时,其接脚为输入(GPxDIR.bit= 0)或输出(GPxDIR.bit=1)。当DSP

重置时,所有I/O预设为数字I/O。

GPxQUAL:输入取样控制缓存器,用来设定做为数字I/O输入(INPUT)

时,其资料的取样率。

GPxDAT:每个I/O端口都有一个数据缓存器(GPxDAT),用来读写接脚的状态。

图15 GPIO方块图。

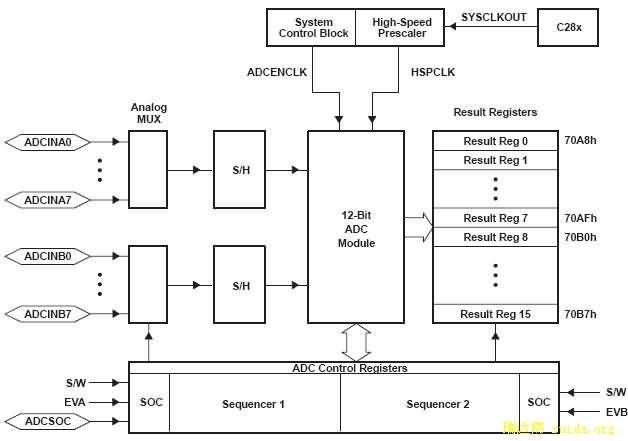

2.7模拟数字转换(Analog-to-DigitalConverter,ADC)模块图16为ADC模块。ADC模块包括内建于取样/ 保持(sample-and-hold,S/H)的12-bitADC,ADC模块功能包括:

1.内建取样/保持(sample-and-hold,S/H)之12位ADC核心

2.模拟输入范围:0.0V~3.0V

3.快速转换速率:80nsat25-MHz ADC clock,12.5 MSPS

4.共16通道(channels)的多任务输入

取得输入模拟电压之数字电压值:

12-bit的ADC模块有25-MHzADC频率于80ns之快速转换,ADC模块有16个信道,可以设定成两个独立的8 信道模块来服务事件管理(EVA,EVB)。

图16ADC模块方块图。

如图17所示为TI建议之连接图,其中若ADC模块的频率操作于1~18.75MHz时ADCRESEXT 的电流偏压电阻使用24.9KΩ,若操作于18.75MHz~25MHz,ADCRESEXT的电流偏压电阻使用20KΩ。本2812数

位控制板之ADC模块希望操作于25MHz,所以需使用20KΩ来做偏压电阻。

图17ADC管脚之连接。

2.8串行通讯接口(SerialCommunicationsInterface,SCI)模块

F2812如图18所示包含两个串行通讯接口(SCI)模块,SCI模块提供了DSP 与其它标准non-return-to-zero(NRZ)格式的异步外围之间的数字通讯。SCI 的接收者和传输者皆采用双总线模式(Double-Buffered),每一个皆有自已独自的允许和中断位。为了保证数据的完整性,SCI有中断侦测、

同位检测、过载和框架错误去检查接收进来的数据。SCI模块主要的功能如

下所示:

1.两个外部的引脚位

.SCITXD:SCI传送输出引脚位

.SCIRXD:SCI接收输入引脚位

2.鲍率有64K种不同的速率,可藉由缓存器设定改变传输速率

3.数据字符(Data-word)格式

.一个开始位

.传输数据位长度格式,可从1到8之间作程序化选择

.奇同位检测/偶同位检测/不使用同位检测的选择

.可选用1或2个停止位

4.四种错误侦测旗标:同位(Parity)、过载(Overrun)、框架(Framing)和中

断(Break)错误侦测

5.可选择使用半双工或是全双工操作模式

6.接收和与传输皆采用双总线模式(Double-buffered)

7.传输方法采用NRZ(non-return-to-zero)格式

图18串行通讯接口(SCI)模块之方块图。

增强型SCI的特色:

自动鲍率侦测硬件逻辑

16-level传输/接收FIFO

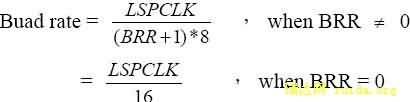

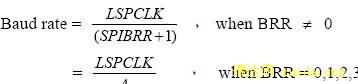

2.9串行外围接口(SerialPeripheralInterface,SPI)模块

F2812如图19所示包含四引脚位串行外围接口(SPI)模块。SPI 模块使用于DSP控制器和外部外围或另一个处理器两者之一的通讯。典型的应用包含外部I/O 或外围延伸装置,例如:移位缓存器、显示装置和ADCs。SPI之Master/Slave操作支持多重装置通讯。

SPI模块装置主要功能共有如下所述:

1.四个外部引脚位:

.SPISOMI:SPIslave-输出/master-输入引脚位

.SPISIMO:SPIslave-输入/master-输出引脚位

.SPISTE:SPIslave传送-允许引脚位

.SPICLK:SPI串行-频率引脚位

2.两个操作模式:Master和Slave

3.鲍率:125个不同可程序速率

4.数据字符(Data-word)长度:1到16个数据位增强型SPI的特色:

16-level传输/接收FIFO

延迟传递控制

图19串行外围接口(SPI)模块之方块图。

2.10Bootloader开机模式

TMS320F2812单芯片提供多种的Boot开机模式供使用者选择和使用,这一小节主要描述Boot开机模式的方法。如表10为Boot 开机模式经由GPIOF中的四个接脚(GPIOF2、3、4、12)在开机时的状态来选择六种的开机动作。

表10Boot模式之GPIOF引脚位状态。

GPIOF4 (SCITXDA) GPIOF12 (MDXA) GPIOF3 (SPISTEA) GPIOF2 (SPICLK) 模式选择 (Mode Selected) 1 X X X 至Flash地址 (0x3F7FF6) 0 1 X X 至外部EEPROM呼叫SPI_Boot下载0 0 1 1 至SCI-A呼叫 SCI_Boot 下载 0 0 1 0 至H0 SARAM地址 (0x3F8000) 0 0 0 1 至OTP地址(0x3D7800) 0 0 0 0 至GPIOB呼叫Parallel_Boot下载

图20Bootloader模式流程图。

如图20为Bootloader模式流程图,下列是Bootloader模式分析。

1.至FlashMemory:

在这个模式中,DSP会先跳去执行内部的FlashMemory地址(0x3F7FF6),所以使用者必需在0x3F7FF6这个地址烧录一段跳至Boot 主程序的机械码,如:LB_c_int00。

2.至H0SARAM:

在这个模式中,BootROM软件将设定F2812装置然后直接跳去地址0x3F8000(在H0SARAM内存方块的第一个地址)。

3.至OTP内存:

在这个模式中,BootROM软件将设定F2812装置然后直接跳去地址0x3D7800(在OTP内存方块之第一个地址)。

4.标准串行Boot模式(SCI):

在这个模式中,经由SCI-A端口加载程序代码到on-chip内存里,执后在内存里执行Boot程序。

5.SPIEEPROMBoot模式:

在这个模式中,经由SPI埠从外部EEPROM加载程序代码和数据到on-chip内存里。

6.从GPIO埠Boot:

在这个模式中,利用GPIOB从外部来加载程序代码和数据,这个模式分别支持8位和16位的数据串。

本文如需正确应用需结合英文原版资料配合查阅

R:读取;R/W:可读可写;-0=重置后的值

NOTE:EALLOW-protected register

表6 LOSPCP 缓存器位元说明表。

位元 名称

功能描述

15-3 Reserved 保留 2-0 LSPCLK这些位元设定低速外围频率比(LSPCLK)与SYSCLKOUT的关系:如果LOSPCP≠0,LSPCLK=SYSCLKOUT/(LOSPCPx2)

如果LOSPCP=0,LSPCLK =SYSCLKOUT

=000,低速频率= SYSCLKOUT/1

=001,低速频率= SYSCLKOUT/2

=010,低速频率= SYSCLKOUT/4( 预设值)

=011 ,低速频率= SYSCLKOUT/6

=100,低速频率= SYSCLKOUT/8

=101,低速频率= SYSCLKOUT/10

=110 ,低速频率= SYSCLKOUT/12

=111 ,低速频率= SYSCLKOUT/14

PCLKCR(外围频率控制缓存器)是用来允许或禁能各个外围模块的频率,当外围要使用时就必需将其频率允许,如此一来外围才能使用,而若不需使用的外围,可以将其频率关掉,如此可以达到节省功率的作用。如表7 所示为PCLKCR缓存器的格式,缓存器的位元说明如表8所示。

表7PCLKCR缓存器位元格式表*。

15 14 13 12 11 10 9 8 Reserved ECAN ENCLK Reserved MCBSP ENCLK SCIB ENCLK SCIA ENCLK Reserved SPI ENCLK R-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

7-4 3 2 1 0 Reserved ADC ENCLK Reserved EVB ENCLK EVA ENCLK R-0 R/W-0 R-0 R/W-0 R/W-0

R:读取;R/W:可读可写;-0=重置后的值

NOTE:EALLOW-protected register

*如果外围区块没有使用,则此外围的频率将可以被关掉已达成最小的电力消耗

表8PCLKCR缓存器位元说明表:

位元 名称

功能描述

15 Reserved 保留14 ECAN ENCLK 如果此位元被设定,在CAN 外围范围内的系统频率将 被致能。在低电力操作下,此位将被使用者或重置设为0。 13 Reserved 保留 12 MCBSP ENCLK 如果此位元被设定,在McBSP外围范围内的低速频率(LSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。 11 SCIB ENCLK 如果此位元被设定,在SCI-B 外围范围内的低速频率(LSPCLK)将被致能。在低电力操作下,此位元将被使用者或经由重置设为0。 10 SCIA ENCLK 如果此位元被设定,在SCI-A 外围范围内的低速频率(LSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。 9 Reserved 保留 8 SPIA ENCLK 如果此位元被设定,在SPI 外围范围内的低速频率(LSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。 7-4 Reserved 保留 3 ADC ENCLK 如果此位元被设定,在ADC 外围范围内的高速频率(HSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。2 Reserved 保留 1 EVB ENCLK 如果此位元被设定,在EV-B 外围范围内的高速频率(HSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。 0 EVA ENCLK 如果此位元被设定,在EV-A 外围范围内的高速频率(HSPCLK)将被致能。在低电力操作下,此位将被使用者或经由重置设为0。2.3内存结构介绍

2.3.1TMS320F2812内存映

如图4为TMS320F2812内存映像。“Low64K”之内存地址范围映像到240x的数据空间地址,”High 64K”之内存地址范围映像到24x/240x的程序空间地址,24x/240x兼容程序代码只能在“High64K”内存区域执行。

图4TMS320F2812内存映像(MemoryMap)。

17

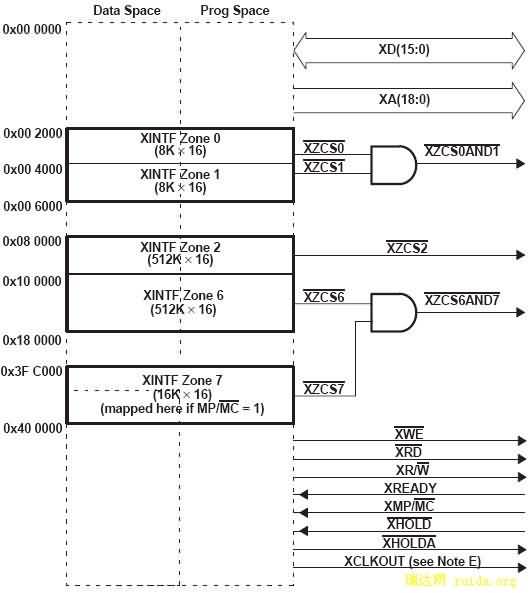

2.3.2外部内存接口(XINTF)

TMS320F2812的外部内存接口(XINTF)是非多任务异步总线,映像到5个固定的内存映像区段,其定义如图5 所示.外部内存接口(XINTF)提供19条地址线及16条数据线,每个区段最

大可以存取的内存范围为512Kx16,所支持的外部内存高达1Mx16

以上。

图5外部内存接口(XINTF)方块图。

2.4 32位元CPU Timers0/1/2

TMS320F2812有3个32位元的CPUTimer,如图7为CPU-Timers之方块图。CPU-Timer0 可以让使用者来应用,而CPU-Timer1和CPU-Timer2则被保留做为实时(Real-Time)OS(例如:DSP-BIOS)。这些CPU-Timers 不同于事件管理模块(EVA,EVB)内一般用途用(General-Purpose)Timers。CPU-Timer大致上的运作如下:32 位元的计数缓存器(TIMH:TIM)加载周期缓存器(PRDH:PRD)的值,计数缓存器是以TMS320F2812的SYSCLKOUT(150MHz)之速率递减,当计数到0时,Timer会产生一个中断信号。

相关IC下载

LC864512—5C77/N801 LA7687A(N201) LA4285(N

AN5195K、AN5199、AN5265、AN5274、AN5521、AN5

AD9883APDF格式参考资料。

BA3880S、BA7001、BA7021等PDF格式参考资料

CTV222S等PDF格式参考资料

CXP84420-X133SP等PDF格式参考资料

KA9258D等PDF格式参考资料

LA4225、LA4285、LA4287、LA7680、LA7688A、LA7

LC863320A、LC864912A、LC864916A、等PDF格式参

M51393AP参考资料