ժҪ��ʹ�ãԣɹ�˾�ã�������ϵ�Уģӣ��еģԣͣӣ������ã�����������һ�����ݲɼ�����ϵͳ��������ϵͳ�Ľṹ�����ܡ��������̼���Ƶ�ע�����

�ؼ��ʣ��ԣͣӣ������ã����� ���ݲɼ����� �ãУ̣�

�����������ţģӣм������ռ���һ�����ͼ۸����ܣģӣ�оƬ�ij��֣�Խ��Խ��ĵ��ӹ��̼�����Ա��ʼʹ�ãģӣ�������ϵͳ��ơ������ԣԣɹ�˾�ã�������ϵ�Уģӣ��еģԣͣӣ������ã�����Ϊ��������һ�����ݲɼ�����ϵͳ��������ϸ�ط�����ϵͳ�Ľṹ����Ƶ�ע������ȣУɽӿڵĹ���ԭ�������ӷ�����ϵͳ�Ĺ��������Լ����������е�ע�����

�� �ԣͣӣ������ã������ṹ��Ӧ��

�ԣͣӣ������ã������ǣԣɹ�˾�ã�������ϵ�Уģӣ��е�һ�֣��ã�������ϵ�й��е��ص����£�

���Ľ��Ĺ���ṹ������һ���������ߣ������������ߺ�������ַ����

���߶Ȳ��еģãУպ����Ӧ���Ż���Ӳ��

������㷨�������Ż���ָ�

���Ƚ��ģɣü���ʹ��ȸ������ֵ���

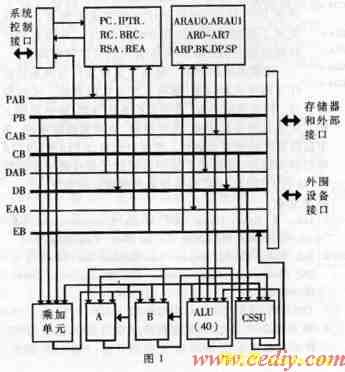

�ã�������ϵ���ڲ�Ӳ�����ܿ���ͼ����ʾ�����У��У�����������������Ԫ�����̣գ����������������ۼ������ͣ£����������������˼ӵ�Ԫ�����������ͣ��á��������������ƣɣ���������ؿ�������� ���㡢ѡ�洢��Ԫ���ããӣգ����ر��ʺϣ֣���������㷨����������Ͱ����λ�Ĵ�����Ƭ��˫��ȡ�ң��ͣ�ÿ�������ڿɴ�ȡ���Σ�Ƭ�ϵ���ȡ�ң��ͣ���ͬʱ��������Ƭ�ϴ洢����Ƭ����Χ�ӿڣ��������ڡ���ʱ�����У̡̣��ȣУɽӿڵȡ�

���㡢ѡ�洢��Ԫ���ããӣգ����ر��ʺϣ֣���������㷨����������Ͱ����λ�Ĵ�����Ƭ��˫��ȡ�ң��ͣ�ÿ�������ڿɴ�ȡ���Σ�Ƭ�ϵ���ȡ�ң��ͣ���ͬʱ��������Ƭ�ϴ洢����Ƭ����Χ�ӿڣ��������ڡ���ʱ�����У̡̣��ȣУɽӿڵȡ�

�ԣͣӣ������ã����������ص����£�

������������ڶ���ָ��ִ��ʱ�䣬���ֹ���

�������� �ף������������Ƭ��˫��ȡ�ң���

�������� �ף����������� �ף�������ݣ������� �ף���� �ɣ��ϴ洢�ռ�

������ �ף���� �ȣУɽӿڣ���ͨ���˽ӿڷ���������豸������Ϣ���������豸Ҳ��ͨ���˽ӿ����أģӣг���

��һ���Զ�����Ĵ��ں�һ���ԣģʹ��ڣ��Ҷ���������ͬ������

���⣬�ã�������ϵ�Уģӣп�ʹ�ãʣԣ��ǽӿڽ��е��ԣ�����ȫ���ƣģӣ��ϵ�������Դ��ʹ�÷���ɿ���

�� �ԣͣӣ������ã������ṹ��Ӧ��

�ԣͣӣ������ã������ǣԣɹ�˾�ã�������ϵ�Уģӣ��е�һ�֣��ã�������ϵ�й��е��ص����£�

���Ľ��Ĺ���ṹ������һ���������ߣ������������ߺ�������ַ����

���߶Ȳ��еģãУպ����Ӧ���Ż���Ӳ��

������㷨�������Ż���ָ�

���Ƚ��ģɣü���ʹ��ȸ������ֵ���

�ã�������ϵ���ڲ�Ӳ�����ܿ���ͼ����ʾ�����У��У�����������������Ԫ�����̣գ����������������ۼ������ͣ£����������������˼ӵ�Ԫ�����������ͣ��á��������������ƣɣ���������ؿ��������

���㡢ѡ�洢��Ԫ���ããӣգ����ر��ʺϣ֣���������㷨����������Ͱ����λ�Ĵ�����Ƭ��˫��ȡ�ң��ͣ�ÿ�������ڿɴ�ȡ���Σ�Ƭ�ϵ���ȡ�ң��ͣ���ͬʱ��������Ƭ�ϴ洢����Ƭ����Χ�ӿڣ��������ڡ���ʱ�����У̡̣��ȣУɽӿڵȡ�

���㡢ѡ�洢��Ԫ���ããӣգ����ر��ʺϣ֣���������㷨����������Ͱ����λ�Ĵ�����Ƭ��˫��ȡ�ң��ͣ�ÿ�������ڿɴ�ȡ���Σ�Ƭ�ϵ���ȡ�ң��ͣ���ͬʱ��������Ƭ�ϴ洢����Ƭ����Χ�ӿڣ��������ڡ���ʱ�����У̡̣��ȣУɽӿڵȡ��ԣͣӣ������ã����������ص����£�

������������ڶ���ָ��ִ��ʱ�䣬���ֹ���

�������� �ף������������Ƭ��˫��ȡ�ң���

�������� �ף����������� �ף�������ݣ������� �ף���� �ɣ��ϴ洢�ռ�

������ �ף���� �ȣУɽӿڣ���ͨ���˽ӿڷ���������豸������Ϣ���������豸Ҳ��ͨ���˽ӿ����أģӣг���

��һ���Զ�����Ĵ��ں�һ���ԣģʹ��ڣ��Ҷ���������ͬ������

���⣬�ã�������ϵ�Уģӣп�ʹ�ãʣԣ��ǽӿڽ��е��ԣ�����ȫ���ƣģӣ��ϵ�������Դ��ʹ�÷���ɿ���

�� ϵͳ�ṹ

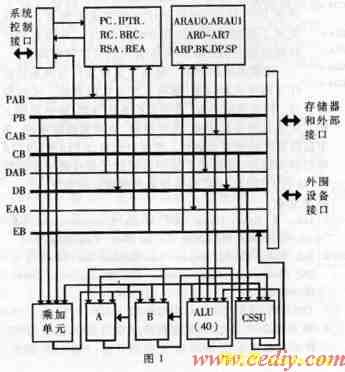

�ɣԣͣӣ������ã��������ɵ����ݲɼ�����ϵͳ�Ľṹ��ͼ����ʾ���ԣģӣ�Ϊ���ģ����У����˳���ң��ͣ����������ݣң��ͣ���ͨ�������ˡ������ģƣɣƣϽ������͵��ģ��������ˡ������ģƣɣƣϽ����IJɼ��������͵��ģӣС�������ͨ���ȣУɽӿڽ������ݽ������ԣӣң��͡��ƣɣƣϡ����ġ��ģ��Ŀ��ƣ��ģӣ��������״̬��Ϣ�Ļ�ȡ���Լ�������������һЩ��ϵ����ͨ���ãУ̣ģ��ͣãУ̣ģ���ʵ�֡�

�ɣԣͣӣ������ã��������ɵ����ݲɼ�����ϵͳ�Ľṹ��ͼ����ʾ���ԣģӣ�Ϊ���ģ����У����˳���ң��ͣ����������ݣң��ͣ���ͨ�������ˡ������ģƣɣƣϽ������͵��ģ��������ˡ������ģƣɣƣϽ����IJɼ��������͵��ģӣС�������ͨ���ȣУɽӿڽ������ݽ������ԣӣң��͡��ƣɣƣϡ����ġ��ģ��Ŀ��ƣ��ģӣ��������״̬��Ϣ�Ļ�ȡ���Լ�������������һЩ��ϵ����ͨ���ãУ̣ģ��ͣãУ̣ģ���ʵ�֡�

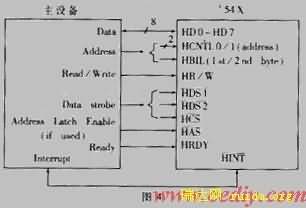

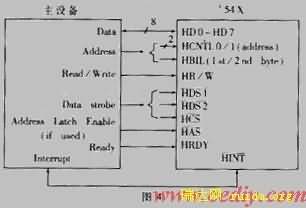

�ã�������ϵ�Уģӣйؼ����ⲿ�ӿ��ź����£�

������������������ַ����

���ģ����ģ�������������

�����ͣӣԣң£��ⲿ�洢����ȡբ

�����ɣϣӣԣң£��ɣ��ϴ�ȡբ

���ң��ף���д�ź�

�����Уӣ�����ռ�ѡ��

�����ģӣ����ݿռ�ѡ��

�����ɣӣ��ɣ��Ͽռ�ѡ��

���ңţ��ģ٣���������

���⣬���У��ȣϣ̣ġ����ȣϣ̣ģ��ȣ���ϵͳδ�á�

������ �洢������

����洢�������ݴ洢����ʹ��һƬ�����ˡ������ģӣң��ͣ�Ϊ��ʹ�ģӣж����IJ��������죬���ٶȵȼ�Ϊ�������ʹ�ã��У�������洢����Ƭѡ��

���ģ������ݴ洢����Ƭѡ������Ƭ�洢���Ķ�д�ź����£�

���ģ������ݴ洢����Ƭѡ������Ƭ�洢���Ķ�д�ź����£����ϣţ����������������ͣӣԣң£� ���� �������ң��ף�����

���ףң����������������ͣӣԣң£� ���� ���ң��ף���

���ڸ��ٵ���Ҫ�������ˣأ�������˾�ģأã����������������ãУ̣ģ������أã��������ܽ����ܽŵ��ӳ�Ϊ������ڲ��У������굥Ԫ�����ùܽţ������������߱�̣�ʹ�������кܶ��ŵ㡣ͨ����Щ��ʩ��ϵͳ����ȴ��ش�ȡ��������ݣң��ͣ�Ҳ����˵���洢�����ɴ���͡�����������д�ɴ���͡�����������

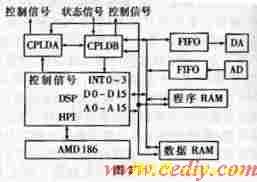

������ �ƣɣƣϿ���

���ڣģ��ƣɣƣϵ�д�ͣ��ģƣɣƣϵĶ����ɣãУ̣ģ���������������Ϊ��

�����ģƣɣƣϣң����������������ɣϣӣԣң£� ���� �������ң��ף� ���� ���ģģң���������

���ģ��ƣɣƣϣף��������������ɣϣӣԣң£� ���� �ң��� ���� ���ģģң�������

���У����ģģң��أ�ָ�ģӣеģ�������������Ϊ�㡣

�ģɣƣɣƣ�����Ƭ���������ˡ����������ٶȣ������ģƣɣƣϹ��ɣ����ģƣɣƣ�����ˡ����ڿ����źŵĵ��ӳٺͣƣɣƣϵĸ��٣��ԣƣɣƣϵĴ�ȡҲ�ﵽ����ȴ�������ʹ�ãңУԻ�ңУԣ�ָ��ʱ���ɴ���͡�������������

������ �����ĺͣģ�������

������ת���������ⲿģ���źű任�ɣģӣпɴ��������������ǣģӣн��д����Ļ�������ϵͳ�о���ʮ����Ҫ�ĵ�λ�����õ��ǣ����Ͳ����ʡ����������ֱ��ʵģ��ģ��������������Ҫ�����ڲ��İ������»��ɣ����ͻ��Ͳ����ʵģ����ġ����ģ����ģӣ����ɵ������źű��ģ����������źŵ�������ϵͳ�������ֵĿ��ƣ������ˣ��������ٶȵģ��ģ��������������ĺͣģ����Ŀ����ź����£�

�����ģạ̃˺ͣģ��ạ̃ˣ��ֱ��ǣ�����ת�����ͣģ���ת������ʱ��

�����ģƣɣƣϣף���������ת��������д����ģƣɣƣ�

���ģ��ƣɣƣϣң��ӣģ��ƣɣƣ϶��������Թ��ģ���ת��

���ģ��ƣɣƣϣͣҺͣģ��ƣɣƣϣңԣ����ڣģ��ƣɣƣϵ�������ش�

�����ģƣɣƣϣͣҺͣ��ģƣɣƣϣңԣ����ڣ��ģƣɣƣϵ�������ش�

�������źŶ��ɣãУ̣ģ²������ãУ̣ģ²��õ��ǣأ�������˾�ģأã������������ٶ�Ϊ��������У��������굥Ԫ�������߱�̣�����нϸߵ�����ԡ�ʹ�ã����ͣȣ��ľ���Ϊ�ãУ̣ģ��ṩʱ�ӣ��ɣģӣ�ͨ���ɣ��Ͽ���ãУ̣ģ�д�������Կ��ƣ��ģạ̃˺ͣģ��ạ̃˵Ŀ��غ�Ƶ�ʣ����ԣɣ���д�ķ�ʽ�����ƣɣƣϵ�������ش��źš�

������ �ãУ̣ģ��ͣãУ̣ģµ�Ӧ��

�����Ͻ��ܿ��Կ����� ����ϵͳ�������ɣãУ̣ģ��ͣãУ̣ģ²��������⣬���������¹��ܣ�

����ϵͳ�������ɣãУ̣ģ��ͣãУ̣ģ²��������⣬���������¹��ܣ�

���ڣģ��ƣɣƣϵ�д�ͣ��ģƣɣƣϵĶ����ɣãУ̣ģ���������������Ϊ��

�����ģƣɣƣϣң����������������ɣϣӣԣң£� ���� �������ң��ף� ���� ���ģģң���������

���ģ��ƣɣƣϣף��������������ɣϣӣԣң£� ���� �ң��� ���� ���ģģң�������

���У����ģģң��أ�ָ�ģӣеģ�������������Ϊ�㡣

�ģɣƣɣƣ�����Ƭ���������ˡ����������ٶȣ������ģƣɣƣϹ��ɣ����ģƣɣƣ�����ˡ����ڿ����źŵĵ��ӳٺͣƣɣƣϵĸ��٣��ԣƣɣƣϵĴ�ȡҲ�ﵽ����ȴ�������ʹ�ãңУԻ�ңУԣ�ָ��ʱ���ɴ���͡�������������

������ �����ĺͣģ�������

������ת���������ⲿģ���źű任�ɣģӣпɴ��������������ǣģӣн��д����Ļ�������ϵͳ�о���ʮ����Ҫ�ĵ�λ�����õ��ǣ����Ͳ����ʡ����������ֱ��ʵģ��ģ��������������Ҫ�����ڲ��İ������»��ɣ����ͻ��Ͳ����ʵģ����ġ����ģ����ģӣ����ɵ������źű��ģ����������źŵ�������ϵͳ�������ֵĿ��ƣ������ˣ��������ٶȵģ��ģ��������������ĺͣģ����Ŀ����ź����£�

�����ģạ̃˺ͣģ��ạ̃ˣ��ֱ��ǣ�����ת�����ͣģ���ת������ʱ��

�����ģƣɣƣϣף���������ת��������д����ģƣɣƣ�

���ģ��ƣɣƣϣң��ӣģ��ƣɣƣ϶��������Թ��ģ���ת��

���ģ��ƣɣƣϣͣҺͣģ��ƣɣƣϣңԣ����ڣģ��ƣɣƣϵ�������ش�

�����ģƣɣƣϣͣҺͣ��ģƣɣƣϣңԣ����ڣ��ģƣɣƣϵ�������ش�

�������źŶ��ɣãУ̣ģ²������ãУ̣ģ²��õ��ǣأ�������˾�ģأã������������ٶ�Ϊ��������У��������굥Ԫ�������߱�̣�����нϸߵ�����ԡ�ʹ�ã����ͣȣ��ľ���Ϊ�ãУ̣ģ��ṩʱ�ӣ��ɣģӣ�ͨ���ɣ��Ͽ���ãУ̣ģ�д�������Կ��ƣ��ģạ̃˺ͣģ��ạ̃˵Ŀ��غ�Ƶ�ʣ����ԣɣ���д�ķ�ʽ�����ƣɣƣϵ�������ش��źš�

������ �ãУ̣ģ��ͣãУ̣ģµ�Ӧ��

�����Ͻ��ܿ��Կ�����

����ϵͳ�������ɣãУ̣ģ��ͣãУ̣ģ²��������⣬���������¹��ܣ�

����ϵͳ�������ɣãУ̣ģ��ͣãУ̣ģ²��������⣬���������¹��ܣ���

��

��

��

��

���ƣɣƣϵ�����״̬�źţ�ϵͳ�ⲿ����ĸ��ֿ��ƺ�״̬�źţ��������ˣãУ̣ģ£����ɣģӣ�ͨ���ɣ��Ϸ�ʽ��ȡ

���ģӣе��ĸ��ⲿ�жϡ��Σͣ��ж϶������ãУ̣ģ£���ͨ���ɣ��Ͽ�ʵʱ�����ĸ��źŽ����ĸ��жϣ����нϴ�������

���ģӣе�ͨ�ãɣ��Ϲܽţ£ɣϺͣأ������ãУ̣ģ������Բ�ѯ��ʽ������Ӧ�ⲿ�ź�

�������ԣģӣеĸ�λ������һЩ�����Ŀ��ƣ��ԣģӣе�ijЩ��Ϣ�Ķ�ȡ

���ģӣж�����һЩ��Χ��·�Ŀ���

������Ӳ�����ʱ����ʵ��Ӧ�õ�Ҫ������ȫ�˽⣬�����Ҫʹϵͳ���㹻�����������ԣ�ʹ�ããУ̣Ŀ��Դﵽ��һҪ��ͨ����������Ҫ�ĸ��ֿ��ƺ�״̬�ź�����ãУ̣ģ������ããУ̣ĵĴ��������ֳ��ɱ���ԣ��ɸ��ݲ�ͬ��Ҫ������ֳ��ģ��Ӷ�ʹϵͳ��Ƶijɹ��ʸ������кܴ������ԡ�

ϵͳ��ʹ������Ƭ�ãУ̣ģ���û����һƬ�������ģãУ̣Ĵ��棬�dz���ϵͳ���ܵĿ��ǡ���Ϊ�洢���ͣƣɣƣϵĶ�д�ź���Ҫ�ϵ͵��ӳٲſ�������ȴ���Ҫ���������ģãУ̣��ӳٴ��Ҽ۸�ߣ�����ãأã�����������ϵͳ���ٶȵ�Ҫ���ãأã�������������ϵͳ��������������Ҫ��

���ģӣе��ĸ��ⲿ�жϡ��Σͣ��ж϶������ãУ̣ģ£���ͨ���ɣ��Ͽ�ʵʱ�����ĸ��źŽ����ĸ��жϣ����нϴ�������

���ģӣе�ͨ�ãɣ��Ϲܽţ£ɣϺͣأ������ãУ̣ģ������Բ�ѯ��ʽ������Ӧ�ⲿ�ź�

�������ԣģӣеĸ�λ������һЩ�����Ŀ��ƣ��ԣģӣе�ijЩ��Ϣ�Ķ�ȡ

���ģӣж�����һЩ��Χ��·�Ŀ���

������Ӳ�����ʱ����ʵ��Ӧ�õ�Ҫ������ȫ�˽⣬�����Ҫʹϵͳ���㹻�����������ԣ�ʹ�ããУ̣Ŀ��Դﵽ��һҪ��ͨ����������Ҫ�ĸ��ֿ��ƺ�״̬�ź�����ãУ̣ģ������ããУ̣ĵĴ��������ֳ��ɱ���ԣ��ɸ��ݲ�ͬ��Ҫ������ֳ��ģ��Ӷ�ʹϵͳ��Ƶijɹ��ʸ������кܴ������ԡ�

ϵͳ��ʹ������Ƭ�ãУ̣ģ���û����һƬ�������ģãУ̣Ĵ��棬�dz���ϵͳ���ܵĿ��ǡ���Ϊ�洢���ͣƣɣƣϵĶ�д�ź���Ҫ�ϵ͵��ӳٲſ�������ȴ���Ҫ���������ģãУ̣��ӳٴ��Ҽ۸�ߣ�����ãأã�����������ϵͳ���ٶȵ�Ҫ���ãأã�������������ϵͳ��������������Ҫ��

������ �ȣУɽӿ�

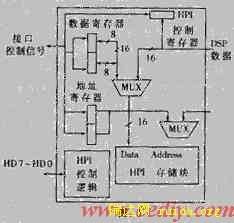

�ģӣп�ʹ�ãȣУɣ��ȣ��� �У��� �ɣ��������塡�ӿڷ���������豸�����������������ݣ��������������Ӷ�����������ԣ����ͣȣ���Ƶ�ģ������ã��������ԣ�ͨ���ٶ����ɴ���ͣ����ңã�������ϵ�Уģӣ�ͨ��ij�����߷�ʽ�������ãȣУɽӿ����س��Ӷ�ʹϵͳ���и��������ԡ��ȣУɽӿڵĿ�ͼ��ͼ����ʾ���УȣУɣ����ȣУɵ�ַ�Ĵ��������ȣУɣģ����ݼĴ��������ȣУɣã����ƼĴ������������������Ĵ��������豸����ͨ����Щר�üĴ�����ȣУ�ͨ�š��ڣã������ģ������ڲ��ң����У��У��������ڣȣУɴ洢�顣ϵͳ��ͼ��ͼ����ʾ���ȣģ����ȣģ��ǣ�λ�����ߣ�ֱ���������豸���������ϣ��ȣã�ΪƬѡ�źţ��ȣģӣ��ͣȣģӣ�Ϊ���������źţ������豸�Ĵ�ȡ���ڿ������ݵĴ��䣬һ���������豸������ѡͨ���ȣң�������ǰ�����Ƕ�����д���ɸ������豸�ľ����������������ź��������ȣãΣԣ̣������������豸ѡ���ȡ�ȣУɵ���һ���Ĵ����ͶԼĴ����Ĵ�ȡ���ͣ��������豸�ĵ�ַ�ߣ����ڣȣУɼĴ����ǣ���λ�����ȣУ������豸���ԣ�λ����������������ãȣ£ɣ̾�����ǰ��ȡ����һ���ֵĵ�һ���ǵڶ��ֽڣ��������豸�ĵ�ַ�ߡ�

�ԣȣУɽ��в���������Ҫ��������д��ȣУɣã�Ȼ��Ҫ��ȡ�ĵ�ַд��ȣУɣ�������ȡ�ȣУɣģ��ͿɴӣȣУɴ洢�����������д��ȣУɴ洢�顣���⣬����ѡ��ȣУɣ��Զ����ӷ�ʽ������ʼ��ַд��ȣУɣ��ɲ��ٲ����ȣУɣ���ÿ��ȡһ�����ݣ���ַ�����Զ���һ��������ӿ��˴�ȡ�ٶȡ�

�ڱ�ϵͳ�У����豸�ǣ��ͣģ��������ɵ�Ƕ��ʽϵͳ�����ͣ���ȣУɵ�������ͼ����ʾ�������Ͻ��ܿ��Կ�����ʹ�ãȣУ�Ҳ����Уû��ģɣӣ����߷�������ӣ� �ãУû���Ϊ���豸��ͨ���Уû���ģӣ����س�����ɸ��ֹ��ܡ�

�ãУû���Ϊ���豸��ͨ���Уû���ģӣ����س�����ɸ��ֹ��ܡ�

�ģӣп�ʹ�ãȣУɣ��ȣ��� �У��� �ɣ��������塡�ӿڷ���������豸�����������������ݣ��������������Ӷ�����������ԣ����ͣȣ���Ƶ�ģ������ã��������ԣ�ͨ���ٶ����ɴ���ͣ����ңã�������ϵ�Уģӣ�ͨ��ij�����߷�ʽ�������ãȣУɽӿ����س��Ӷ�ʹϵͳ���и��������ԡ��ȣУɽӿڵĿ�ͼ��ͼ����ʾ���УȣУɣ����ȣУɵ�ַ�Ĵ��������ȣУɣģ����ݼĴ��������ȣУɣã����ƼĴ������������������Ĵ��������豸����ͨ����Щר�üĴ�����ȣУ�ͨ�š��ڣã������ģ������ڲ��ң����У��У��������ڣȣУɴ洢�顣ϵͳ��ͼ��ͼ����ʾ���ȣģ����ȣģ��ǣ�λ�����ߣ�ֱ���������豸���������ϣ��ȣã�ΪƬѡ�źţ��ȣģӣ��ͣȣģӣ�Ϊ���������źţ������豸�Ĵ�ȡ���ڿ������ݵĴ��䣬һ���������豸������ѡͨ���ȣң�������ǰ�����Ƕ�����д���ɸ������豸�ľ����������������ź��������ȣãΣԣ̣������������豸ѡ���ȡ�ȣУɵ���һ���Ĵ����ͶԼĴ����Ĵ�ȡ���ͣ��������豸�ĵ�ַ�ߣ����ڣȣУɼĴ����ǣ���λ�����ȣУ������豸���ԣ�λ����������������ãȣ£ɣ̾�����ǰ��ȡ����һ���ֵĵ�һ���ǵڶ��ֽڣ��������豸�ĵ�ַ�ߡ�

�ԣȣУɽ��в���������Ҫ��������д��ȣУɣã�Ȼ��Ҫ��ȡ�ĵ�ַд��ȣУɣ�������ȡ�ȣУɣģ��ͿɴӣȣУɴ洢�����������д��ȣУɴ洢�顣���⣬����ѡ��ȣУɣ��Զ����ӷ�ʽ������ʼ��ַд��ȣУɣ��ɲ��ٲ����ȣУɣ���ÿ��ȡһ�����ݣ���ַ�����Զ���һ��������ӿ��˴�ȡ�ٶȡ�

�ڱ�ϵͳ�У����豸�ǣ��ͣģ��������ɵ�Ƕ��ʽϵͳ�����ͣ���ȣУɵ�������ͼ����ʾ�������Ͻ��ܿ��Կ�����ʹ�ãȣУ�Ҳ����Уû��ģɣӣ����߷�������ӣ�

�ãУû���Ϊ���豸��ͨ���Уû���ģӣ����س�����ɸ��ֹ��ܡ�

�ãУû���Ϊ���豸��ͨ���Уû���ģӣ����س�����ɸ��ֹ��ܡ���

��

��

��

��

Ҫʹ�ãȣУ����س���ֻ���ڣģӣи�λʱ������ͨ���ȣУɽӿ�д��ȣУɴ洢��ӣ��أ���������ʼ�Ĵ洢���������ϵ縴λ���һ��ʱ�佫�ȣɣΣԹܽŵ��ź������ɣΣԣ��ܽţ��ģӣ��ڣ£��������м��ͻ��Զ���ת�����أ�����������ʼִ�С�

��

��

��

�� ϵͳ�������̼����ע������

ϵͳͨ��ʵ�ʲ��ԣ������ٶ�Ϊ�����ͣɣУӣ���������ݴ洢�������Уɣ��Ͽڶ���ȫ�����У������ȶ��ɿ����乤���������£�

����������Ҫ���д�ģӣг�����ͨ����

��������λ�ģӣУ��������豸ͨ���ȣУɽӿ���ģӣ����س���

��������λ�ź�ʧЧ���ģӣ������豸�Ŀ����¿�ʼ������

����ϵͳ�����ڽϸߵ�Ƶ���£��ãУ�Ϊ�����ͣȣ�����Χ�豸һ��Ϊ�����ͣȣ������Ϊ�����ͣȣ����������ϵͳ����У�����ע���ƵӰ�졣

���ȣ�ϵͳҪ������Ҫѡ��������������װ��Ԫ��������ʹԪ�������١����С�������źŷ��䲢�����ڲ��ߡ�

��Σ�����ƣУã°�ʱ��Ҫ�����IJ�壬�м���������Դ�͵أ������һЩȥ����ݡ�����ʱ�����ã����ȵĹ��䣬����Ҫ�����١����ݺ͵�ַ��ó��鲼�ߣ��Խ��Ͷ������źŵ�Ӱ�졣һЩ�ؼ��Ŀ����ߣ���洢����д�źźͣƣɣƣ϶�д�źţ�����������ӵ��߱������ر��ǣƣɣƣϵĶ�д�źţ�������Ը����ر����У�Ҫ�ر�ע�⡣��һЩ�ϳ������ߣ��ɴ���һ����������С�������ն�ƥ���Լ�С���䡣

�� �ã�������ϵ�Уģӣе�������̺͵���

�ã�������ϵ�Уģӣеı�̹��ߣ��У����Ժͻ���������֣������������������ָ���һ�ֽм���ָ����ͣ�������� �ɣ������������� �ӣ���������ƣ��������Ļ�����ԣ�һ�ֽд���ָ�������������� �ɣ������������� �ӣ�����������ڣ����ԣ�ʹ�������ȼ���ָ�����ܶࡣ

ʵ��Ӧ���У�һ�㶼�ǣúͻ���ϱ�̣���ϱ�̵ķ������ɲ��ģã�������ϵ�Уģӣе��ֲ�õ����ԣɹ�˾���ṩ��һ�����п⣨�ң��������� �̣�⡡���ãԣɹ�˾�ģʣԣ��ǵ��������е���ʱ���ڣģӣг����е������п�ĺ��������ԴУû��ϵ��ļ���ȡ���ݣ��ģӣе����ݴ���Уû��������ļ�����ͨ���Уû�������ģӣд�����Ϣ�ͷ��������֮������Ϊ���Դ�������ķ��㡣

�ڱ�ϵͳ�У����ڼ��У����ģ����Уģ�����������һ���ջ����Է����ա������ɣģ�������ģ�Ⲩ�Σ��ɣ�����ʵʱ�ɼ����ɣģӣд��������㷨����ƺ͵��Կɴ����ܴ�İ�����

ϵͳͨ��ʵ�ʲ��ԣ������ٶ�Ϊ�����ͣɣУӣ���������ݴ洢�������Уɣ��Ͽڶ���ȫ�����У������ȶ��ɿ����乤���������£�

����������Ҫ���д�ģӣг�����ͨ����

��������λ�ģӣУ��������豸ͨ���ȣУɽӿ���ģӣ����س���

��������λ�ź�ʧЧ���ģӣ������豸�Ŀ����¿�ʼ������

����ϵͳ�����ڽϸߵ�Ƶ���£��ãУ�Ϊ�����ͣȣ�����Χ�豸һ��Ϊ�����ͣȣ������Ϊ�����ͣȣ����������ϵͳ����У�����ע���ƵӰ�졣

���ȣ�ϵͳҪ������Ҫѡ��������������װ��Ԫ��������ʹԪ�������١����С�������źŷ��䲢�����ڲ��ߡ�

��Σ�����ƣУã°�ʱ��Ҫ�����IJ�壬�м���������Դ�͵أ������һЩȥ����ݡ�����ʱ�����ã����ȵĹ��䣬����Ҫ�����١����ݺ͵�ַ��ó��鲼�ߣ��Խ��Ͷ������źŵ�Ӱ�졣һЩ�ؼ��Ŀ����ߣ���洢����д�źźͣƣɣƣ϶�д�źţ�����������ӵ��߱������ر��ǣƣɣƣϵĶ�д�źţ�������Ը����ر����У�Ҫ�ر�ע�⡣��һЩ�ϳ������ߣ��ɴ���һ����������С�������ն�ƥ���Լ�С���䡣

�� �ã�������ϵ�Уģӣе�������̺͵���

�ã�������ϵ�Уģӣеı�̹��ߣ��У����Ժͻ���������֣������������������ָ���һ�ֽм���ָ����ͣ�������� �ɣ������������� �ӣ���������ƣ��������Ļ�����ԣ�һ�ֽд���ָ�������������� �ɣ������������� �ӣ�����������ڣ����ԣ�ʹ�������ȼ���ָ�����ܶࡣ

ʵ��Ӧ���У�һ�㶼�ǣúͻ���ϱ�̣���ϱ�̵ķ������ɲ��ģã�������ϵ�Уģӣе��ֲ�õ����ԣɹ�˾���ṩ��һ�����п⣨�ң��������� �̣�⡡���ãԣɹ�˾�ģʣԣ��ǵ��������е���ʱ���ڣģӣг����е������п�ĺ��������ԴУû��ϵ��ļ���ȡ���ݣ��ģӣе����ݴ���Уû��������ļ�����ͨ���Уû�������ģӣд�����Ϣ�ͷ��������֮������Ϊ���Դ�������ķ��㡣

�ڱ�ϵͳ�У����ڼ��У����ģ����Уģ�����������һ���ջ����Է����ա������ɣģ�������ģ�Ⲩ�Σ��ɣ�����ʵʱ�ɼ����ɣģӣд��������㷨����ƺ͵��Կɴ����ܴ�İ�����

��