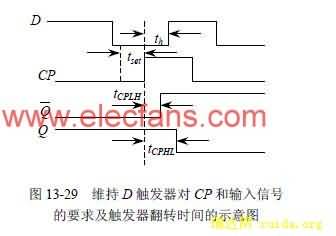

根据前面分析可知,维持阻塞D触发器的工作分两个阶段,在CP=0时,为准备阶段;CP由0向1正向跳变时刻为状态转移阶段。为了使维持阻塞D触发器(见图13-22)能可靠工作,要求:

在CP正跳变触发沿到来之前,门F和门G输出端Q2和Q1应建立起稳定状态。由于Q2和Q1稳定状态的建立需要经历两个与非门的延迟时间,这段时间称为建立时间tset=2tpd。在这段时间内要求输入激励信号D不能发生变化。所以CP=0的持续时间应满足tCPL≥tset=2tpd。

在CP正跳变触发沿来到后,要达到维持阻塞作用,必须使Q4或Q3由1变为0,这需要经历一个与非门延迟时间。在这段时间内,输入激励信号D也不能发生变化,将这段时间称为保持时间th,其中th=1tpd。

CP=1的持续时间tCPH必须大于tCPHL。该触发器的tCPHL为三级与非门(C→A→B或E→B→A)延迟时间,即tCPH>tCPHL=3tpd。

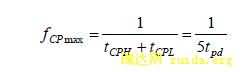

CP脉冲的工作频率应满足

维持阻塞D触发器对输入信号D及触发脉冲CP的要求示意如图13-29所示。