打印本文

打印本文  关闭窗口

关闭窗口 【性能 参数】

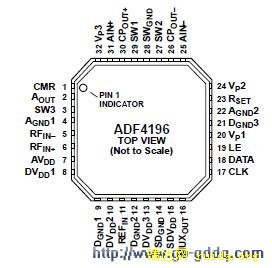

采用32脚LFCSP封装,超快建立时间的6GHz小数N分频PLL,专门设计用来满足通信基础设施和脉冲多普勒雷达应用的GSM/EDGE锁定时间要求。结合外部环路滤波器和VCO使用时,可以实现低于5us的锁定时间。它由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。

特点:

在5us内完成整个GSM频段上的跳频,相位建立时间低于20us

相位误差:1°rms(4GHzRF输出)

数字可编程输出相位

三线式串行接口

片内低噪声差分放大器

相位噪声品质因数:-216dBc/Hz

引脚排列图:

打印本文

打印本文  关闭窗口

关闭窗口