打印本文

打印本文  关闭窗口

关闭窗口 【性能 参数】

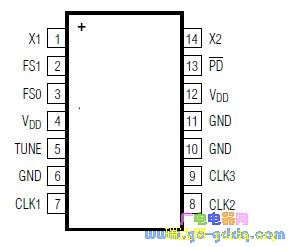

采用14引脚TSSOP封装,+3.3V电源,输入参考频率:5MHz至50MHz,参考源:晶体或输入时钟,两路N分频反馈PLL(4MHz至200MHz),带缓冲输出,两路参考时钟缓冲输出,提供OTP用于工厂预设PLL频率(请联系工厂),通过I?C接口或3电平FS引脚设置视频或音频时钟,低PLL抖动:45MHz时14ps,集成±200ppm调谐范围的VCXO,输出一组通用的音频时钟。

引脚排列图:

打印本文

打印本文  关闭窗口

关闭窗口  打印本文 打印本文  关闭窗口 关闭窗口 |

|

| MAX9472来源于瑞达科技网 | |

| 作者:佚名 文章来源:不详 点击数 更新时间:2012/7/7 文章录入:瑞达 责任编辑:瑞达科技 | |

|

|

|

|

【性能 参数】 采用14引脚TSSOP封装,+3.3V电源,输入参考频率:5MHz至50MHz,参考源:晶体或输入时钟,两路N分频反馈PLL(4MHz至200MHz),带缓冲输出,两路参考时钟缓冲输出,提供OTP用于工厂预设PLL频率(请联系工厂),通过I?C接口或3电平FS引脚设置视频或音频时钟,低PLL抖动:45MHz时14ps,集成±200ppm调谐范围的VCXO,输出一组通用的音频时钟。 引脚排列图:

|

|

打印本文 打印本文  关闭窗口 关闭窗口 |