打印本文

打印本文  关闭窗口

关闭窗口 关键词:Tn402,TN752

1 引言

超大规模数字电路中的时钟信号,是数字电路系统中的关键因素之一。电路中,要求时钟信号具有较大的灵活性,如周期的占空比可以在很宽的范围内进行调节,具有良好的自适应带宽特性等。根据对时钟信号的不同要求,其生成方法各不相同,如高精度的锁相环频率发生器、新型CMOS注入锁定振荡器电路和VCO等。相对而言,多谐振荡器则是低成本实现方法,非常适合于ASIC单元电路的应用。本文以提高频率稳定性、降低功耗为目标,完成一种多谐振荡器的优化设计。

2 多谐振荡器电路原理分析

从功能上讲,多谐振荡器比环型振荡器优越。环型振荡器的结构如图1所示,依靠奇数个倒相器的闭环系统实现振荡输出。每个倒相器的等效输出电阻为R,输出电容为C,由n个倒相器依靠延时获得的频率为f=1/nRC。可以看出,由于芯片面积的限制,倒相器的面积和个数受到限制,故频率调节不灵活,误差较大,并且电路的最大缺点是无法实现宽范围占空比的调节。

利用电容和电阻的充放电延时,可实现宽周期的占空比的输出调节。采用多谐振荡器电路设计简单,占用面积小。根据电阻跨接方式的不同,可分为两种形式,其结构如图2所示。一种是电阻跨接一个倒相器,另一种是电阻跨接三个倒相器,它们的振荡原理是相同的。

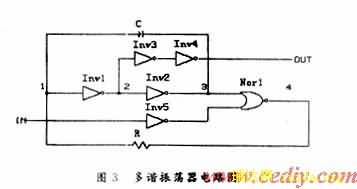

以其中的一种结构为例,具体电路如图3所示,包括电阻R、电容C、倒相器Inv2...Inv5和或非门Nor1。Inv3和Inv4起输出驱动作用。从输出端IN输入逻辑电平0,设置起振条件,起振后IN变为并保持逻辑电平1。Nor1等效为倒相器,这样三个倒相器Inv1、Inv2和Nor1与R、C一起形成振荡回路,输出端OUT将保持稳定的方波波形。通过调整Inv1、Inv2和Nor1三个器件中PMOSNMOS的宽长比和R、C值,可实现不同周期和占空比的方波。

随着时间的推移,结点1电位因电容C放电而逐渐变低,只要地点1的电位不低于Vtr,Inv1不会跳变,其它结点的电位不变,即结点2一直输出低电平。当点1的电位小于Vtr时,Inv1开始翻转,重新转入状态a。显然,稳定后系统进入状态a与状态b的循环变化中,形成振荡输出,临界点为结点1电压Vtr点。

3 多谐振荡器优化设计

3.1 周期调节

周期调整包括粗调和细调。粗调是指调整电阻和电容的大小,以确定振荡周期的范围,为了使振荡器稳定工作,需要细调Inv1和PMOS1和NMOS1的宽长比。Inv2和Inv3对周期的影响很小可以忽略。设输出端点2保持高电平的时间为T1,保持低电平的时间为T2,通过计算可得振荡器周期为[1](公式忽略了倒相器本身延时的影响)。

式中:Vtr1为Inv1的转折电压。Vtr1定义为NMOS1和PMOS1电流相等时的输入电压,即[1]

VTN、VTP分别为NMOS1、PMOS1阈值电压的绝对值,Vtr1与增益因子KN1和KP1有关,即与Inv1的宽长比有关。通常有KN1=KP1,好Vtr1=1/2Vdd。由式(1)可得T=2.2RC。由于R、C和Inv1的延时均存在一定范围的限制,故多采用此结构形成中低频方波振荡器。

3.2 占空比调节

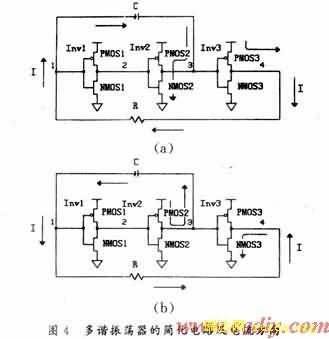

图3简化后可得如图4所示的结构。图中的倒相器均采用倒宽长比设计,以减小驱动电流,增大延时,达到需要的振荡周期。根据电路中电流的方向,可分为两种状态。结点1为低电平时,为状态a(包括起振时的状态)。结点2是输出端口,电流方向如图3(a)所示。由于结点2为高电平,Inv2的NMOS2导通;结点3为低电平,Inv3的PMOS3导通,电流经电源(Vdd)流过R、电容C,Inv2的NMOS2流入地(Gnd)。随着时间的推移,结点1因对电容C充电而使电位逐渐抬高,只要其电位不超过Vtr,Ivn1状态就不会跳变,其它结点的电位不会变动,即结点2保持高电平输出。

当结点1的电位充电大于Vtr时,转入状态b。Inv1开始翻转,在此临界点,结点1的电压比结点3高Vtr,跳变后节点3为高电平。由于电容两端的电压不能突变,所以结点1的电压最高可变为Vdd+Vtr。电流方向如图3(b)所示。由于结点2为低电平,Inv2的PMOS2导通;结点3为高电平,Inv3的NMOS3导通,所以电流从Inv2的PMOS2电源(Vdd)流出,经过电容C、电阻R,Inv3的NMOS3地流入(Gnd)。

除Vtr1影响占空比之外,Inv1、Inv2对占空比有很大的影响。占空比不同的周期信号,主要依靠调整Inv的宽长比来获得。

Inv3的NMOS3的宽长比,相当于增大导通电阻,即延长电容放电时间,导致输出低电平时间增加,即占空比变小。相反,增加宽长比,会使占空比变大。

单向调整会使电路的性能不稳定,如电压和温度变化时,如电压和温度变化时,会使占空比发生很大的变化,所以较好的方法是对称调节,即在减小Inv2的PMOS2的Inv3的NMOS3的宽长比的同时,增加Inv2的NMOS2和Inv3的PMOS3的宽长比以提高电路性能的稳定性。设电流流过PMOS3、NMOS2、PMOS2和NMOS3的延迟时间分别为t1、t2、t3和t4,则T1=t1+TRC+t2,T2=t3+TRC+t4,TRC=RC。宽长比越大对电流的延时越大,所以调节占空比只需调整上述四个MOS管的宽长比。

3.3 功耗调节

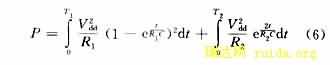

功耗的大小和振荡器的有效电阻有关,电阻大则功耗小。因此,尽量调整电阻,以降低功耗。振荡回路的功耗中,Inv的动态功耗较小可忽略。设图3(a)回路的有效电阻为R1,图3(b)回路的有效电阻为R2,一个振荡周期的功耗为[2]

各Inv的沟道电阻和宽长比W/L成反比[3],即r∞L/KW,设PMOS2、NMOS2、PMOS3和NMOS3的沟道电阻分别为rp2、r2、rp3和rn3,则可得R1=R+rn2+rp3,R2=R+rp3+rn3,在调整占空比的同时也影响功耗的大小,所以振荡器的优化设计在于各项技术指标的综合分析。

3.4 多谐振荡器的调节步骤和设计方案

由于多谐振荡器各主要参数之间存在相互影响,因此在优化策略上应有所考虑。此处可按以下四个步骤进行:

(1)调节Inv1的阈值电压,使得Vtr1=1/2Vdd,这样Vtr1对占空比的调节不会产生影响。

(2)调节占空比,主要依靠调节Inv2、Inv3。由Inv2、Inv3的调节可以使占空比的范围达到20%~80%,如果需要此范围以外的占空比,可以通过调节Vtr1。如需要10%的占空比,可以调节Vtr1=1/3Vdd,再调节Inv2、Inv3;如需要90%的占空比,可以调节Vtr1=2/3Vdd,然后调节Inv2、Inv3。

(3)调节周期。主要依靠调节R、C、Inv1。在调节Inv1时,保证Inv1的转折电压为1/2Vdd。

(4)调节功耗。主要是尽量降低R和Inv2、Inv3的沟道电阻。但必须在保证周期和占空比参数的前提下。

由于这几个参数指标调节是相互影响的,调整过程中,有时会遇到模拟不收敛的现象,需重新调整。

多谐振荡器的设计指标如下:振荡电路工作频率为250kHz,最低、正常和最高工作电压分别为2.7V、3V和3.3V;最低、正常和最高温度分别为-10℃、25℃和60℃。要求在上述条件下,振荡频率变化范围在15%之内。该模拟用的是上华0.8uSPSM工艺,VTN、VTP分别是-0.93V、0.836V。

调节Inv1的阈值电压,取Vtr1=1/2Vdd,由式(5)计算可得,βn=2.7βp[1],所以(Wp/Lp)/(Wn/Ln)=4.96。设Wp=Wn=3.5μ,得到Ln/Lp=4.96,取Ln=25,Lp=5。模拟可得如下波形。从图5可以看出Vtr1=1/2Vdd。

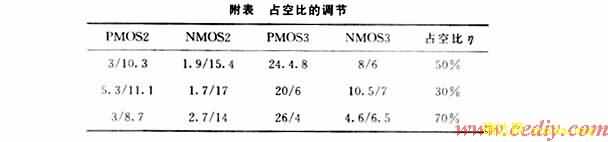

调节占空比:PMOS和NMOS的宽长比与占空的关系如附表所示。

调节频率:粗调电阻和电容,R=200kΩ,C=0.1pF,通过HSPICE模拟测得周期T=4μs。通过T=2.2RC计算可得T=4.4μs。周期调节和理论计算基本一致。如下图所示:

周期和占空比的调节已达到要求,还要进一步调节功耗。可以成比例的减小电阻,增大电容。调节R=540kΩ,C=0.03pF。模拟后功耗从65.667μW下降至17.039μW,至此,电阻和电容不能再调节,不然会引起模拟不收敛。

进一步验证调节结果在不同温度和电压下是否达到要求。如果不行,需重新调节频率和功耗。验证结果如表2所示。

4 结论

多谱振荡器的原理分析上已不存在问题。但在振荡器参数指标的设计上存在很大的困难。关键是要对各项技术指标进行综合分析,从而确定最佳方案。但对工作频率在吉赫以上的多谱振荡器来说,无论在振荡电路的设计,补偿网络的设置,性能指标的高度与测量及结构工艺的安排等诸多方面需要研究的问题仍很多。

参考文献

[1] 高德远,康继昌编.超大规模集成电路系统的电路的设计原理[M].西北工业大学出版社,1989

[2] 龙沪强,陈昌发等.新型数控振荡器[J].上海交通大学学报,1999

[3] 纪宗南.数控振荡器[M].南京航空航天大学自动控制系,1999

[4] 主文焕.汪蕙主编.模拟电路的计算机分析与设计PSPICE程序应用[M].精华大学出版社.1997

[5] 赵雅兴主编.电子线路HSPICE分析和设计[M].天津大学出版社,1995

打印本文

打印本文  关闭窗口

关闭窗口