打印本文

打印本文  关闭窗口

关闭窗口 关键词:倍流整流;磁集成;拓扑

引言

在现今的大电流DC/DC变流器中,倍流整流(CDR)拓扑结构由于它本身的特点,已经成为最优的输出整流拓扑选择。与传统的带中间抽头的整流拓扑相比较,其变压器副边只有一组绕组,结构上相对比较简单;同时CDR副边绕组的匝数也较少,在大电流情况下,副边绕组的损耗就会降低;且它的输出有两个滤波电感,流经每个电感上的电流只有负载电流的一半,所以,输出滤波电感上的功率损耗也较小,由于两个滤波电感的存在,变流器的输出电流/电压纹波也相对较小。但它需要3个磁性元件,必然导致体积的增大,从而减小了功率密度;同时具有较多的连接端子,在电流较大时,连接端子上的功率损耗必然相对较大。为了克服以上缺点,磁集成(integrated magnetics)技术早已应用在CDR拓扑当中。所谓磁集成就是将变流器中两个或两个以上的分立磁性元件(变压器,输入/输出滤波电感)都绕制在一副磁芯内,从而达到减小体积,提高功率密度,减少连接端子的目的。

图1

本文对多种磁集成倍流整流拓扑(IM-CDR)进行了分析和比较,选出了其中较佳的拓扑,并在此IMCDR拓扑的基础上对一个输出为1V,20W的DC/DC变流器进行了实验,同时给出了实验波形。特别要提出的是,当负载较大时,存储在变压器原边漏感中的能量可用来实现副边同步整流管的自驱动,从而降低了控制电路的复杂程度。

1 几种磁集成倍流整流拓扑的比较

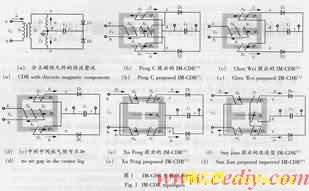

图1给出了到目前为止的几种适于低压大电流电压调整模块(VRM)拓扑的IM-CDR拓扑结构。

图1(a)所示的是采用分立元件构成的CDR电路,它一共需要3个分立的磁性元件,分别是输出滤波电感L1和L2,以及变压器。结果导致变流器体积和重量过大。同时,它的大电流连接端子也较多,这必然增加副边的导通损耗。

图2

为了避免上述这种传统CDR拓扑结构的不足,PengC提出了一种IM-CDR电路拓扑[1],如图1(b)所示。它将以往的CDR整流电路中的3个分立磁性元件(输出滤波电感和变压器)集中绕制在同一副磁芯中,结果大大地减小了变流器的体积和重量,但是,由于它副边仍然有较多的绕组数和连接端子,使得这种CDR拓扑的应用受到了限制。

图1(c)是由Chen Wei提出的CDR拓扑结构[2]。它是将图1(b)中的变压器副边绕组分解,分别绕在磁芯的两个外磁柱上。结果使得拓扑副边的结构变得简单,连接端子也相对减少。这种CDR拓扑结构非常适合大电流变流器的应用场合,因为它含有较少的连接端子和绕组数。且由于它的中心磁柱上有气隙存在,原边的激磁电感Lm就会减小,在输出轻载时能够实现主开关的ZVS[2]。但气隙不能开得太大,如果太大Lm就会很小,导致变压器原边的激磁电流的增大,从而增大原边的导通损耗。

图1(d)中给出的是中心柱不开气隙的情况,此时变压器原边激磁电感Lm较大,原边绕组中的激磁电流较小,因此,原边的导通损耗也较小。在这种IM-CDR拓扑中,由于原副边绕组是分别绕在三个磁柱上的,所以,原副边绕组间的耦合较差,导致变压器原边漏感较大,降低了变流器的性能。此外,这种中间没有气隙两边开气隙的IM-CDR拓扑,其磁芯的生产比较困难。普通的EE或EI磁芯的两个外磁柱上都没有气隙,要应用于图1(d)中的IM-CDR拓扑,就必须在外磁柱上加气隙,结果使得它的实现比较困难。

图3、4

Xu Peng提出了如图1(e)所示的IM-CDR电路拓扑[3]。它是将图1(d)中的变压器原边绕组拆分,并分别绕制到磁芯的两个外磁柱上,这样原副边绕组就会形成较好的耦合。并只是在中心的磁柱加气隙,两个外磁柱上不加气隙。改进的IM-CDR不仅减小了变压器原边漏感,提高变流器性能,而且这种磁芯结构也更加便于生产,普通的EE和EI磁芯就可以满足要求,还有利于减小磁芯损耗和提高效率[3]。但它的原边存在两组绕组,结构要比图1(c)及图1(d)中的拓扑复杂。

在上面提出的这些IM-CDR拓扑中都存在同一个问题,就是它们的输出滤波电感值受到了限制,所以,存在相对较大的输出电流/电压纹波。因此,Sun Jian提出了如图1(f)所示的电路。从结构上与图1(e)相比较,只是在中心的磁柱上加了一组绕组,并串在了输出端,这就相当于在输出端多加了一个滤波电感,从而减小了输出电流和电压纹波[4]。但这种结构拓扑并不适合低压大电流场合。

综上所述,图1(c)所示的IM-CDR拓扑是最简单的,在对输出电流/电压纹波要求不是很高的大电流变流器中,它是最合适的。虽然变压器的原边存在相对较大的漏感,但折衷考虑,它还是最优的选择。而且在负载电流较大的情况下,变压器漏感可用来实现副边同步整流管的自驱动。

2 实验及其结果

IM-CDR结构选择如图1(c)所示的拓扑。从结构上可以看出,磁芯的3个磁柱上都加了相同的气隙(lg),这必然会导致变压器原边的漏感(Lk)的增大,但可以利用变压器原边漏感中的能量实现副边同步整流管的自驱动(开通),同步管的关断是通过外加驱动信号来完成的。实验电路如图2所示,由图2可以看到副边同步管的驱动电路包括一个绕组(Na),两个二极管(Da1,Da2)和两个MOS管(Sa1,Sa2),它的实现比较简单,只需要在磁芯的中心磁柱上多加一组绕组即可。变压器原边采用的是对称半桥拓扑。实验电路的具体参数见表1所列。实验波形图如图3和图4所示。图3是在负载电流Io=4A时测得的变压器原边电压波形以及两个同步整流管的门极驱动电压波形图。由于此时的负载电流较小,反映到变压器原边的激磁电流也较小,在原边开关管关断的瞬间,变压器原边漏感(Lk)与开关管输出结电容(Co1,Co2)间的振荡尖峰不够高,不足以开通副边的同步整流管。所以,在两个原边开关管都处于断态期间内,其中一个同步整流管的体二极管必须导通进行续流。由于此时的负载电流不大,体二极管上的功率损耗也不明显。随着负载的加大,原边的振荡会逐渐增大,直到能够开通副边同步整流管。图4所示的是负载电流Io=20A时的变压器原边电压波形以及两个同步管驱动波形。当原边开关管关断时,存在于漏感中的能量足够以开通两个同步管。然而同步管的关断只能通过外加驱动信号来实现。它们分别来自于原边开关管的门极驱动vg1和vg2。图5是测得的变流器的效率曲线图。

表1 实验电路参数

参 数 数 值

输入电压Vin DC48V

输出电压Vo 1V

输出电流Io 20A

工作频率fs 315kHz

C1,C2 63V/100μF

S1,S2 IRLU2905

SR1,SR2 IRLR7843

Sa1,Sa2 IRLU120

Da1,Da2 IN4148

磁芯(Core) R-42216-EC

气隙(lg) 0.09mm

原边激磁电感L 76μH

原边漏感Lk 0.8μH

变比Np:Ns 10:01

变比Ns:Na 5:01

3 结语

倍流同步整流拓扑在大电流变流器中的应用越来越广泛,但是,传统的结构上存在着磁性元件较多,体积较大等缺点,为了克服这些不足之处,磁集成技术早已经应用在这种拓扑当中。本文分析比较了几种磁集成倍流整流拓扑结构,并给出了相应的实验电路模型。在负载较大情况下,存储在变压器的原边漏感中的能量可以用来实现副边同步整流管自驱动(开通)。

打印本文

打印本文  关闭窗口

关闭窗口