打印本文

打印本文  关闭窗口

关闭窗口 摘 要:本文分析了深亚微米下超大规模SoC的电源设计中存在的问题,给出了业界适用的设计、验证方法,并以工程设计为例,给出层次性SoC设计中电源设计、验证的适用流程。

引言

SoC(系统芯片)是现代微电子技术向前发展的必然趋势。与工艺技术逐步先进的变化相适应,SoC芯片上的内核逻辑的供电电压也逐步降低。供电电源电压减小的一个显著好处是使整个芯片的功耗降低,然而它同时也带来了芯片噪声容限降低的负面影响。芯片供电电源网络上的一个很小的电压波动或毛刺噪声,都可能引起芯片逻辑功能的误动作,或者影响芯片逻辑动作的速度,降低了芯片的性能。因此,电源设计显得比以前更加重要和困难。随着半导体工艺向更高节点发展,由于电源设计的问题所导致的整个芯片性能达不到预期要求甚至完全失败的比例越来越高。据不完全统计:在目前的0.18um和更精细的工艺下,有79%的集成电路设计会遇到电源设计问题,而有高达54%的设计会因此而失败。可*的电源设计已经成为SoC设计成功与否的关键因素之一而加以考虑。

SoC中的电源设计与分析

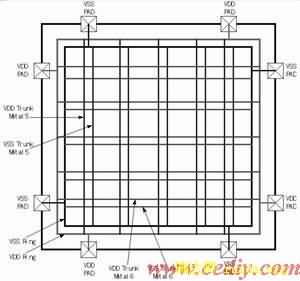

通常,在SoC模块的布局阶段(信号布线之前)完成整个SoC芯片的电源设计,然后根据后续的分析验证结果加以修正。首先,根据SoC芯片的面积和功耗要求,确定所需的电源凸点(PAD)的数目。然后,在选定的用作电源布线的金属层上(一般是最上面两层)每隔一定的间距做一个电源的分支(power-trunk),这样最终形成一个上下两层纵横交错的网格结构,我们称之为电源网格power-grid。典型的电源网格设计如图1所示(以六层金属工艺为例)。

在0.25mm工艺以前,一般都将芯片上的电源网格(包括电源信号和地信号)当作理想网络,芯片上任何地方的电源线的电压都是相等的、稳定的,其大小等于SoC芯片外部所供给的电源电压,而电流的大小可以为任何值。对于地线,也是同样的假定。实际上,尤其当集成电路工艺演进到今天的0.18um及以下的超深亚微米时,包括电源网络在内的所有互连线的阻抗特性表现的就非常明显了。用集总参数的电路观点来看,芯片上的互连线就是各种电阻R、电容C和电感L的组合。从而导致了互连线的时序延迟以及导致了电源网络上的电压波动,电压值将不再是稳定不变的单一值了,这就是我们要讨论的电源电压降(IRdrop)和地电压上升或者反弹(ground-bounce)。(简单起见,以下的“电源”包括电源信号VDD和地信号VSS;“IRdrop”包括VDD上的电压降和VSS上的电压反弹。)

除了电压波动以外,电源网络连线上所能承受的电流能力也是电源设计中必须加以考虑的问题。对于作为互连线的金属层来说,在一定的制造工艺下,在它上面所能允许流过的最大电流是有一定的限度的,否则过大的电流将会导致金属连线熔断,导致芯片失效。这种现象我们称之为电迁移EM(electromigration)。

图1 典型的SoC电源网格

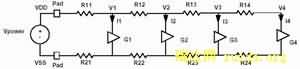

图2 SoC设计中典型的电源网络

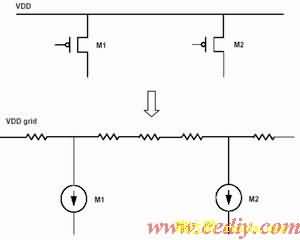

图3 电源分析中的等效模型

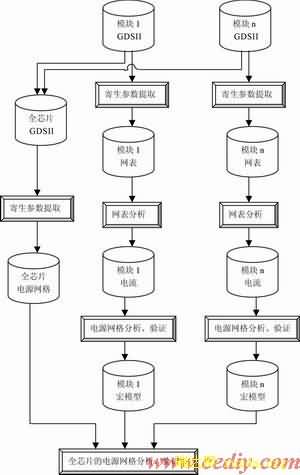

图4 基于宏模块的层次性电源网格验证流程

电压降IRdrop

IRdrop是指出现在集成电路中电源和地网络上电压下降的一种现象。集成电路通常会假设在芯片内的电源为理想电源,它能在瞬间给芯片上的所有门单元(也包括宏单元)提供足够大的电流从而使芯片上的电压保持为统一的值。实际上,由于金属连线的宽度越来越窄,导致它的电阻值上升,所以在整个芯片范围内将存在一定的IRdrop。IRdrop的大小将依赖于从电源凸点到所计算的逻辑门单元之间的等效电阻的大小。

如图2所示,外部电压源连接到SoC芯片的电源凸点上,R11到R14是电源网格VDD上的等效电阻值,R21到R24是电源网格VSS上的等效电阻值,G1到G4是连接在电源和地之间的逻辑门单元。理想情况下,当对这些逻辑门单元进行仿真时,V1到V4都被认为等于VDD,地电压等于VSS。

实际上,电源网格上的真实的电阻值并不是0。例如当有开关动作时,逻辑门单元G4的电压在任何时候都要比VDD值小。从外部电源流到G4的电流一定流过整个电源分布网络,导致产生V=IR的电压降。地信号VSS上的IRdrop是指逻辑门单元G1到G4处地(VSS)电压的上升。

图2同时也说明了电源网格和IRdrop的复杂性。假设逻辑门单元G4的电源凸点处的电压为VDD,G4所消耗的电流为I4安培,而其它逻辑门单元的电流都为0,电流I4通过电源网格从外部电源流向G4。那么逻辑门单元G4处的VDD上的IRdrop就是:

IRdropG4=I4×(R11+R12+R13+R14) (1)

同样,逻辑门单元G2的 VDD上的IRdrop为:

IRdropG4=I4×(R11+R12) (2)

因此SoC设计中的每一个逻辑门单元的电流都会对设计中的其它逻辑门单元造成不同程度的IRdrop。如果连接到金属连线上的逻辑门单元同时有翻转动作,那么因此而导致的IRdrop将会很大。假定图2中G1到G4的瞬态电流分别为I1到I4,那么在G4处的IRdrop就是I1、I2、I3和I4在相应网格电阻产生的电压降之和。

IRdrop可能是局部性的,也可能是全局性的。当相邻位置的一定数量的逻辑门单元同时有逻辑翻转动作时,就引起局部的IRdrop现象。而当芯片某一区域内的逻辑动作导致其它区域的IRdrop时,称之为全局现象。一般来说,当电源网络中的电流大致相等时,从芯片中央到芯片的边缘,各个潜在的IRdrop会构成一圈圈的圆环,而芯片中心部分的潜在IRdrop最大。流过芯片的电流越大,这些不同IRdrop环的范围就会越大。

IRdrop的公式说明了设计中的不同的逻辑门单元在不同时间进行逻辑翻转的重要性。芯片上任何地方的峰值IRdrop要比均值IRdrop可能大得多。但随着SoC芯片的面积的逐步增大,峰值IRdrop与均值IRdrop的比率正逐步趋于一致,因为在一个很大的SoC中很多门单元同时翻转的概率在急剧减小。同步翻转导致IRdrop噪声的主要因素是时钟、总线信号、信号引脚的翻转,它们可能会有很多的门单元同步翻转从而产生了IRdrop问题。

IRdrop的问题表现在常常类似一些时序甚至可能是信号完整性问题,集中显现在如下方面:1) 功能故障:在芯片工作时,如果全局IRdrop过高,则逻辑门就出现功能故障。2) 间歇性的或随数据变化的功能失效:局部IRdrop是比较敏感的,它在一些特定的条件下可能会引起逻辑功能失效。3) 逻辑时序不正常:如果全局IRdrop变化,但还不至于导致系统的逻辑错误,则表现为系统的时序问题。

电迁移EM

金属电迁移是一个通用词汇,表示导致芯片上金属互连线断裂、熔化等的一些失效原因。导致金属电迁移问题的主要原因是金属的长期损耗和金属本身的焦耳热原理。从某种特定意义上来说,电迁移是芯片金属互连线长期损耗的结果。焦耳发热是一种同电迁移相关联的特定问题。焦耳发热是指由于很高的交流电流而导致金属连线某一特定段发热过大。为了减小电迁移的影响,某一特定层的金属连线常常用多层不同材料的金属线以一种三明治的结构加以构造。一般额外的连线层,通常是三明治结构中的最上层和最下层,有更强的抗电迁移能力,能够帮助整个金属连线不至于全部断掉。由于电迁移是一个长期损耗的累积结果,那么一段金属连线的电迁移的危险程度常常用流过这段连线的一定时间内的平均电流来加以测量。

电迁移常常表现出经过一段时间后芯片有时序或功能性的错误。如果芯片中的某一根连线是唯一的,那么当发生电迁移问题以后,会导致整个芯片的功能失效。如果一些连线本来就有冗余设计的考虑,例如电源网络,当发生电迁移问题后,其中的一部分连线会断开,而其它部分的连线就会承受较大的IRdrop问题。如果因为电迁移而导致了线路间的短路,那就是整个芯片的失效。

电源验证工具和流程

Simplex公司提供了一整套电源分析、验证的工具VoltageStorm,能够帮助设计工程师可*地完成整个电源设计。例如,提取电源网格上的寄生参数,并将设计中的每一个MOSFET等效为一个电流源,如图4所示。计算出每个MOSFET的分流电流(tap-current),然后用VoltageStorm对电源网格做IRdrop和EM方面的分析验证,并产生最后分析的结果以备工程师检查所设计的电源网格是否符合预期要求。

VoltageStorm同时支持层次性的设计,对某一模块分析后的结果可以产生VoltageStorm的格式库,直接作为下一级设计的输入,这样可以节省下一级设计的分析时间。一般流程如图4所示。VoltageStorm支持命令格式文件流程,设定好相关参数,例如分析需要的库文件,设计中每个元件的功率文件,所需要分析的电源网络名字及其电压大小等等,就可以运用VoltageStorm完成整个分析验证。

结语

当IC工艺越来越精细,SoC的规模越来越大时,对电源设计的要求就越高。SoC设计必须考虑到可能出现的IRdrop和EM的问题,在具体工艺参数的要求下,精心设计,并运用适当的电子设计自动化(EDA)工具进行全面的分析验证,以确保最后生产的硅芯片能够按设计的预期要求那样可*、稳定、正确地工作。■

参考文献:

1. H. Chang, L. Cooke, M. Hunt, G. Martin, A. McNelly, and L. Todd,‘Surviving the SOC Revolution - A Guide to Platform-Based Design’, Kluwer Academic Publishers, 1999

2. Michael Keating, Pierre Bricaud, ‘Reuse Methodology Manual (For System-On-A-Chip Designs), 3nd Edition’, Kluwer Academic Publishers, 2001

3. VoltageStorm Hierarchical PGS Manual, Cadence

打印本文

打印本文  关闭窗口

关闭窗口