打印本文

打印本文  关闭窗口

关闭窗口 案例1

相位节点上的振荡或振鸣会产生两种负面影响。振荡期间的峰值电压会超过MOSFET数据表中VDSS最大值的80%,这是工程人员考虑可靠性时应遵守的典型准则。振鸣是辐射和传导信号的来源,会在敏感的数字线路上产生噪声,或使系统无法通过EMI测试。

针对以上问题的解决方法如下:

1.同时减缓高边FET电压的上升和下降速度 (添加R1)

2.只减缓高边FET电压的上升速度 (添加Rboot)

3.降低施加在高边FET栅极上的驱动电压 (添加C1或降低VCC)

4.降低施加在低边FET栅极上的驱动电压 (降低VCC)

5.减小低边FET的回路面积,以降低回路电感 (LDRV 到 PGND的回路)

6.选择先进的MOSFET封装以减少寄生电感,Lp = Lss + Ldd

7.选择具有较低Qrr值的MOSFET;该Qrr值是 Coss的一部分,并对Cp有贡献

要降低HDRV引脚的驱动电压,C1约等于Cboot / 5 是很好的起步点。可串联两个升压二极管来降低VCC,进而降低驱动电压。要降低LDRV到PGND回路的电感,可让驱动器靠近低边晶体管。要减小低边FET源极 (Ldd) 到 PGND的回路电感,可在PGND 铜层和源极间增设近路连接。

可根据MOSFET (封装和独立的器件特性) 和线路布局,决定使用以上任何组合。

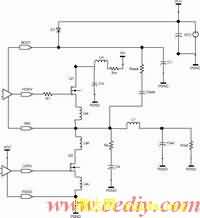

图1同步降压等效电路

如图1所示,HDRV电压降低太多,在HDRV引脚电压之上的开关节点信号会引起高边晶体管的栅-源电压下降,在此期间出现一次或多次低于Vgs(th) 的情况,就会带来更高的开关损耗,降低效率。

图2 Q1导通和Q2关断时的升压过渡

图3 导通波形,其中t1 到 t3

间产生开关损耗

从图2和图3可以看出:Q1不只一次穿过有源区 (t2-t3) 以及阻抗区 (t4-t5)。这意味着高边晶体管产生了额外的开关损耗。通过减小或省掉C1来增加HDRV电压,可降低这个额外的开关损耗。

当上述措施无效时,通常会采用RC 缓冲电路。RC缓冲电路 (即图1中Rs 和 Cs组成的电路) 可按如下步骤实现:

1.在未添加RC 缓冲电路的降压器上加入负载。探测开关节点或低边MOSFET,直到观察到共振,找出开关节点上升沿的共振频率 (fo1)。在测量开关节点时,应在探针上使用短线接地引脚,以便将回路电感引起的错误减至最少。

ωo1 = 2πfo1 = [1]

2.在低边FET的漏极到源极间跨接一个电容(Cadd),然后再重新确定共振频率 (fo2)。

ωo2 = 2πf o2 = [2]一旦获得 fo1 和 fo2 ,就可导出Cadd 和Cp间的关系。可以验证如下的关系:

fo1 / 2 = fo2 ; Cadd = 3Cp [3]

fo1 x 0.75 = fo2 ; Cadd = (9/7) Cp [4]

MOSFET数据手册一般都不包含引脚电感值。PSPICE仿真模型并不能反映真实的布线电感。建议在确定Cp后,用方程 1 来计算Lp。

3.为了使RC缓冲电路具备临界阻尼响应性能,应恰当选取Rs。可根据串联RLC电路的自然响应性能方程来确定Rs,即:

Q = [5]

Q = 1;临界阻尼响应

Q > 1;欠阻尼响应性能-希望缓冲电路超前响应Lp、Cp 振荡

Q < 1;过阻尼响应性能-希望缓冲电路滞后响应Lp、Cp 振荡

可选用Q=1时计算出来的Rs值。调整Rs可在开关节点上获得所希望的阻尼电平。

4.许多关于缓冲电路的文献建议Cs ≥ 2Cp,但这会在Rs上产生额外且难以接受的功率损耗。根据平均功率损耗公式 (参见步骤5),Cs的选择显然是影响功率损耗的重要因素。因此,对于重视效率的设计,必须进行折中,即取Cp < Cs < 2Cp。

5.在选取Rs的额定功率时,可考虑Cs在充电和放电周期中存储的峰值能量。

w = (Cs Vin2) / 2

wtotal = (Cs Vin2)

由于能量随时间变化,平均功率损耗应为:

Pd ~ Cs Vin2 fsw [6]

6.如果第1至第5步的措施还不能抑制振荡,就需要检查输入滤波电路的稳定性。根据R.D. Middlebrook发表的文献摘要,若下式成立,则可实现稳定性或非振荡条件:

[7]

这里,D = Vout/Vin ,方程 7 降低了输入L和C电路共振频率附近的Q值。

案例2

高于低边晶体管阈值Vgs的栅极冲击电压会造成低边和高边FET同时导通。这会在每个开关循环产生重复性短路。虽然每个循环的交叉导通时间只有5~10ns,但时间一长便会导致热失控,使FET超过其最大允许结温。在相位节点上的大电压变化dv/dt、Cgd 和Cgs电容比值、Qrr及驱动电路的反偏阻抗都会产生栅极冲击电压。

MOSFET驱动器中的自适应栅极驱动电路能够大幅缩短死区时间,同时防止潜在的交叉导通电流。当高边和低边晶体管同时导通时,会建立一个从输入电压端到地的低阻抗信道,通常,这会对采用较小芯片的高边晶体管形成较大的应力 (选用较小的芯片是为了将开关损耗减至最少)。相比采用较大芯片的低边晶体管,采用较小芯片的高边晶体管会先达到功率耗散限度。自适应栅极驱动电路虽然是智能化的,但它只能从HDRV、LDRV和开关引脚获取电压信息,从而做出开关转换的决定。由于不能读取内部VGS,因此它不知道晶体管是否完全导通或关断。此外,下面的因素也进一步限制了自适应栅极驱动电路防止交叉导通的能力。

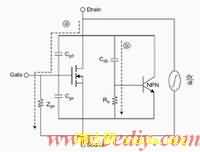

图4 N信道MOSFET的等效电路

当低边晶体管出现电压变化 (dv/dt) ,将会产生两个电流通道。在图4中,沿信道 (a) 的电流在晶体管内部栅极产生额外的Vgs。

Igs = Cgd dv/dt [8]

Igs = Vgs / Zgs [9]

τ= Zgs (Cgd + Cgs)

这里,Zgs=下拉电阻 + HDRV 和MOSFET栅极间的外接电阻 + MOSFET内部栅极电阻。

v(t) = Vin-Vin× e ^ (-t /τ)

dv/dt = (Vin /τ) ×e ^ (-t /τ)

结合方程 8 和 9 可计算出 Vgs,即

Vgs = Zgs Cgd (Vin /τ)×e ^ (-t /τ) =Vin [Cgd / ( Cgd + Cgs )]×e ^ (-t /τ )

当t趋近于0,Vgs = Vin * [ Cgd / ( Cgd + Cgs )] [10]

在上升沿时间t,dv/dt方程中的t趋近于0,栅极上Vgs近似增量可由方程 10 给出。这意味着较大的Cgd会在dv/dt事件出现期间,增大低边晶体管上额外的栅极冲击电压。

此外,沿信道 (b) 的电流会因寄生晶体管导通而导致雪崩击穿,当寄生晶体管因dv/dt事件而导通,双极器件的击穿电压会下降到BVCBO的50%-60%。dv/dt 对寄生双极器件的影响由下式给出:

dv/dt = Vbe / (Rb * Cdb)

在高边和低边晶体管均关断的开关循环中,低边体二极管会导通,而少数电荷则聚集在体二极管中。由图1可知,该电流沿L1、Cout和Q2的体二极管方向流动。当Q1导通时,二极管的反向恢复电流 (Irr) 带走体二极管中的少数电荷。体二极管这种恢复特性可通过跨接低边晶体管Q2的dv/dt观察到。

当今的驱动器具有较低的下拉阻抗 (<1 ?,能满足人们对大芯片和低Rds(on) 晶体管不断增长的需求。LDRV的下拉阻抗低,更突显了具有高栅极内阻Rg晶体管的特性,当LDRV降低时,驱动器将根据在LDRV上观察到的电压做出决定。 由于不同IC供应商的自适应栅极驱动电路有差异,因此处理开关转换过程的方案也会不同。

选择适当的晶体管不仅意味着要观察Qg 和 Rds(on),还需要研究其它参数,如Cgs、Cgd、 Qrr和 Rg。晶体管与MOSFET驱动器的相互作用可能导致晶体管损坏或灾难性失效。在本文所叙述的某些条件下,交叉导通或dv/dt事件也可能导致功率耗散。

通过适当设计输入滤波电路和选择适当的RsCs值可以控制开关节点上的振荡。透过合理布局,以及恰当地选取MOSFET和驱动器,可以将交叉导通减至最少。在无法实现理想布局的情况下,本文讨论的设计建议可有助于改善性能。■

打印本文

打印本文  关闭窗口

关闭窗口