摘 要:本文提出一种新的电流极限可调状态机电路,用于含有PFM控制器和功率MOSFET的单片电源管理集成电路,以设置电流极限值。采用自适应方式和电流极限比较器相结合,使其工作在安全工作区。模拟结果表明本状态机具有高响应度、低误动作等特点。

关键词:电流极限比较器 频率调制 脉宽调制

A Current Limit Regulated State Machine Circuit

Abstract:A kind of state machine circuit is presented which can be used in switching power integrated circuit combining of PFM controller and power MOSFET. it is used to set current limit value and make chip work in safety work area integrated with current limit comparator in method of adaptation After simulating, it is stated that the state machine have the characters of high responsibility and low error action

Key words:current limit comparator, pulse frequency modulate, pulse width modulate

1 引 言

最新研制成功的单片电源管理集成电路采用PWM、PFM混合调制的方式,使开关的响应速度更快,在不同的负载状况下电源均能保持较高的效率。

在当今流行的单片电源管理集成电路中集成了高压功率MOSFET和低压控制电路。功率MOSFET导通后电流逐渐上升,导致功耗增大,必须通过电流极限比较器来关断功率MOSFET。传统的PWM方式中电流极限值固定,无法反映负载的变化,导致在轻负载时效率极低。Power Integration在其最新的TNY26X系列中提出状态机,但响应度不高,且电路设计比较复杂。本文提出一种新的电流极限值可调状态机(Current Limit Regulated State Machine,简称CLRSM)具有高响应度和低误动作等特点。电流极限值与外接负载紧密相关,当外接负载较重时,通过增加功率MOSFET导通时间以便输出更多能量维持次级线圈的稳定,所以需要增大电流极限值以推迟关断时间;当外接负载较轻时,通过减小功率MOSFET导通时间以便输出较少能量维持次级线圈的稳定,此时需要较小电流极限值加快关断功率MOSFET。

2 CLRSM的设计

2.1 逻辑设计

CLRSM是一个离散时域系统,通过侦测负载的随时间的连续变化,获取离散的状态,每个动作的转换都依靠负载的改变或者保持。CLRSM记录下每个时刻负载的状况,通过电阻网络将数值量Q0Q1Q2转换为模拟量给电流极限比较器,电流极限比较器根据该数值量设置电流极限值,从而达到对功率MOSFET导通和关断的时间的调整,实现了负载对整个电源系统输出能量的反馈调节,最终实现了开关电源的高效率。

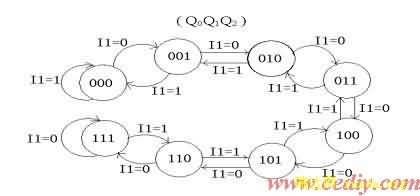

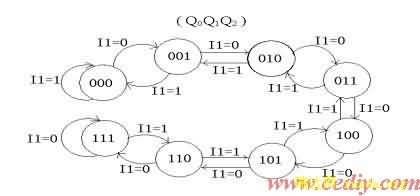

本状态机包括一组状态、状态之间的一组转换,或是状态转换或是状态转换的一组动作组成。状态机被定义为M-{I,O,S,f,h}。其中S-{Si}表示一组状态集合;I-{Ij}表示一组输入信号;O-{Omk}表示一组输出信号;f(Si,a):S×I→S为状态转移函数;h(Si,a):S×I→Omk为输出函数。一个状态机的一个状态转移全过程中,每个当前状态下产生的当前控制信号组成一串有条不紊的控制流,严格控制整个系统的执行。基本的状态机方框图如图1所示,状态转换图如图2所示。

关键词:电流极限比较器 频率调制 脉宽调制

A Current Limit Regulated State Machine Circuit

Abstract:A kind of state machine circuit is presented which can be used in switching power integrated circuit combining of PFM controller and power MOSFET. it is used to set current limit value and make chip work in safety work area integrated with current limit comparator in method of adaptation After simulating, it is stated that the state machine have the characters of high responsibility and low error action

Key words:current limit comparator, pulse frequency modulate, pulse width modulate

1 引 言

最新研制成功的单片电源管理集成电路采用PWM、PFM混合调制的方式,使开关的响应速度更快,在不同的负载状况下电源均能保持较高的效率。

在当今流行的单片电源管理集成电路中集成了高压功率MOSFET和低压控制电路。功率MOSFET导通后电流逐渐上升,导致功耗增大,必须通过电流极限比较器来关断功率MOSFET。传统的PWM方式中电流极限值固定,无法反映负载的变化,导致在轻负载时效率极低。Power Integration在其最新的TNY26X系列中提出状态机,但响应度不高,且电路设计比较复杂。本文提出一种新的电流极限值可调状态机(Current Limit Regulated State Machine,简称CLRSM)具有高响应度和低误动作等特点。电流极限值与外接负载紧密相关,当外接负载较重时,通过增加功率MOSFET导通时间以便输出更多能量维持次级线圈的稳定,所以需要增大电流极限值以推迟关断时间;当外接负载较轻时,通过减小功率MOSFET导通时间以便输出较少能量维持次级线圈的稳定,此时需要较小电流极限值加快关断功率MOSFET。

2 CLRSM的设计

2.1 逻辑设计

CLRSM是一个离散时域系统,通过侦测负载的随时间的连续变化,获取离散的状态,每个动作的转换都依靠负载的改变或者保持。CLRSM记录下每个时刻负载的状况,通过电阻网络将数值量Q0Q1Q2转换为模拟量给电流极限比较器,电流极限比较器根据该数值量设置电流极限值,从而达到对功率MOSFET导通和关断的时间的调整,实现了负载对整个电源系统输出能量的反馈调节,最终实现了开关电源的高效率。

本状态机包括一组状态、状态之间的一组转换,或是状态转换或是状态转换的一组动作组成。状态机被定义为M-{I,O,S,f,h}。其中S-{Si}表示一组状态集合;I-{Ij}表示一组输入信号;O-{Omk}表示一组输出信号;f(Si,a):S×I→S为状态转移函数;h(Si,a):S×I→Omk为输出函数。一个状态机的一个状态转移全过程中,每个当前状态下产生的当前控制信号组成一串有条不紊的控制流,严格控制整个系统的执行。基本的状态机方框图如图1所示,状态转换图如图2所示。

图1 状态机方框图

S-{Si}:{S0,S1,S2,S3,S4,S5,S6,S7}

I-{Ij}:{I1}

O-{Omk}:{000,001,010,011,100,101,110,111}

状态转移函数:f(Si,I1)= (1)

(1)

输出函数:h(Si,I1)= (2)

(2)

本状态机不仅与当前状态有关,而且与当前输入信号I1有关,每次clk到来时状态发生一次变化。

图2 状态转换图

2.2 电路设计

基于以上对于电流极限状态机的定性分析,状态机电路考虑完全采用数字电路来实现。

结合前面的系统框架,Q0、Q1、Q2一起表示状态机处于某种状态,从“000”到“111”总共有八种状态编码分别表示负载的八种状态,从“000”到“111”表示负载逐渐加重,反过来则表示负载逐渐减轻。LOAD=0为重负载,LOAD=1为轻负载。一个周期为5个时钟周期。LOAD=0维持几个周期表示重载后几个周期,状态编码依次增加;LOAD=1维持几个周期表示轻载后几个周期,状态编码依次减小。

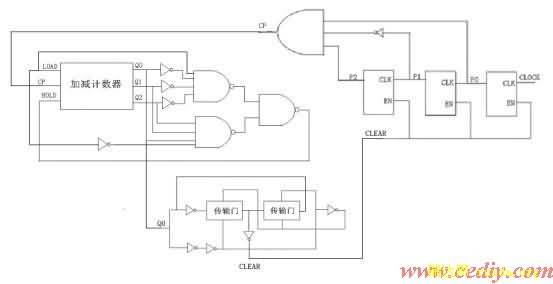

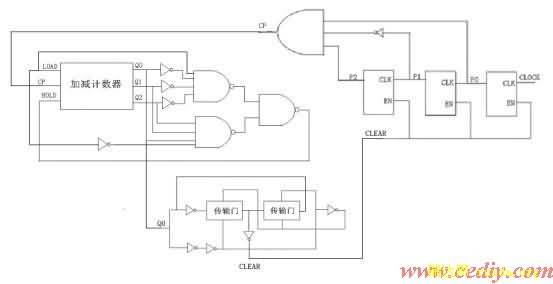

整个状态机由计时器、加减计数器、复位电路组成。逻辑框图如图3所示。LOAD是负载反馈信号;CP是计时器的输出信号,上升延有效;HOLD是状态保持信号;计时器完成每次状态转换间隔时间的计算,经过五个时钟周期后CP翻转一次送入加减计数器。加减计算器在每次CP到来后改变状态。如果LOAD=0而且Q0Q1Q2=“111”,则状态机输出保持不变;如果LOAD=1而且Q0Q1Q2=“000”,则状态机输出也保持不变。复位电路是在每次状态改变后给计时器发送一个清零的信号,使计时器复位,计时器重新计时。

S-{Si}:{S0,S1,S2,S3,S4,S5,S6,S7}

I-{Ij}:{I1}

O-{Omk}:{000,001,010,011,100,101,110,111}

状态转移函数:f(Si,I1)=

(1)

(1)输出函数:h(Si,I1)=

(2)

(2)本状态机不仅与当前状态有关,而且与当前输入信号I1有关,每次clk到来时状态发生一次变化。

图2 状态转换图

2.2 电路设计

基于以上对于电流极限状态机的定性分析,状态机电路考虑完全采用数字电路来实现。

结合前面的系统框架,Q0、Q1、Q2一起表示状态机处于某种状态,从“000”到“111”总共有八种状态编码分别表示负载的八种状态,从“000”到“111”表示负载逐渐加重,反过来则表示负载逐渐减轻。LOAD=0为重负载,LOAD=1为轻负载。一个周期为5个时钟周期。LOAD=0维持几个周期表示重载后几个周期,状态编码依次增加;LOAD=1维持几个周期表示轻载后几个周期,状态编码依次减小。

整个状态机由计时器、加减计数器、复位电路组成。逻辑框图如图3所示。LOAD是负载反馈信号;CP是计时器的输出信号,上升延有效;HOLD是状态保持信号;计时器完成每次状态转换间隔时间的计算,经过五个时钟周期后CP翻转一次送入加减计数器。加减计算器在每次CP到来后改变状态。如果LOAD=0而且Q0Q1Q2=“111”,则状态机输出保持不变;如果LOAD=1而且Q0Q1Q2=“000”,则状态机输出也保持不变。复位电路是在每次状态改变后给计时器发送一个清零的信号,使计时器复位,计时器重新计时。

图3 状态机逻辑框图

加减计数器是一个带控制端的八进制加减计数器,如图3所示。HOLD是状态保持信号, 。加减计数器的功能见表1。

表1 加减计数器功能表

CP HOLD LOAD 工作状态

× Q0Q1Q2=“000” 1 保持

Q0Q1Q2=“000” 0 加法运算

× Q0Q1Q2=“111” 0 保持

Q0Q1Q2=“111” 1 减法运算

0 0 加法运算

0 1 减法运算

加减计数器是一个带控制端的八进制加减计数器,如图3所示。HOLD是状态保持信号, 。加减计数器的功能见表1。

表1 加减计数器功能表

CP HOLD LOAD 工作状态

× Q0Q1Q2=“000” 1 保持

Q0Q1Q2=“000” 0 加法运算

× Q0Q1Q2=“111” 0 保持

Q0Q1Q2=“111” 1 减法运算

0 0 加法运算

0 1 减法运算

表1 加减计数器功能表

3 电路仿真结果与讨论

在ORCAD中做了如下一些仿真。假设LOAD为固定的周期信号,从S0到S7八种状态的仿真结构如图4.1-4.8所示。LOAD为输入波形,U26:QA、U26:QB、U26:QC分别代表Q0、Q1、Q2。设定初始Q0Q1Q2为“000”,负载LOAD的周期为1ms,时钟周期T=10us,经过5个时钟周期后,Q0Q1Q2状态变化一次。做瞬态分析,仿真时间为3ms。仿真结果表明输出逻辑随状态和负载的变化关系。

图4.1-图4.4为负载较重的情况,在LOAD的低电平期间Q0Q1Q2完成了从S0到S7八种状态转换后保持在S7状态,到达LOAD高电平时,分别从S7状态向S6、S5、S4、S3状态转换,高电平时间越长,状态转换次数越多。当LOAD回到低电平后,状态又重新恢复。

图4.5-图4.8为负载较轻的情况,在LOAD的低电平期间Q0Q1Q2完成了从S0到S4、S3、S2、S1的状态转换,到达高电平后,分别从S4、S3、S2、S1回到S0状态,低电平时间越长,状态转换次数越多。

在ORCAD中做了如下一些仿真。假设LOAD为固定的周期信号,从S0到S7八种状态的仿真结构如图4.1-4.8所示。LOAD为输入波形,U26:QA、U26:QB、U26:QC分别代表Q0、Q1、Q2。设定初始Q0Q1Q2为“000”,负载LOAD的周期为1ms,时钟周期T=10us,经过5个时钟周期后,Q0Q1Q2状态变化一次。做瞬态分析,仿真时间为3ms。仿真结果表明输出逻辑随状态和负载的变化关系。

图4.1-图4.4为负载较重的情况,在LOAD的低电平期间Q0Q1Q2完成了从S0到S7八种状态转换后保持在S7状态,到达LOAD高电平时,分别从S7状态向S6、S5、S4、S3状态转换,高电平时间越长,状态转换次数越多。当LOAD回到低电平后,状态又重新恢复。

图4.5-图4.8为负载较轻的情况,在LOAD的低电平期间Q0Q1Q2完成了从S0到S4、S3、S2、S1的状态转换,到达高电平后,分别从S4、S3、S2、S1回到S0状态,低电平时间越长,状态转换次数越多。

图4.1 LOAD信号每个周期中低电平为950us,高电平为50us

图4.2 LOAD信号每个周期中低电平为850us,高电平为150us

图4.3 LOAD信号每个周期中低电平为800us,高电平为200us

图4.4 LOAD信号每个周期中低电平为720us,高电平为

图4.5 LOAD信号每个周期中低电平为280us,高电平为720us

图4.6 LOAD信号每个周期中低电平为200us,高电平为800us

图4.7 LOAD信号每个周期中低电平为150us,高电平为850us

图4.8 LOAD信号每个周期中低电平为100us,高电平为900us

状态数量越多将越精确的表示负载的轻重程度,但将会增加电流极限值的调整次数和电路复杂度,状态数量太少又不能精确表示负载状况,CLRSM采用折中和优化的方法即保证了负载反映的精确又使响应度高。

4 结 论

通过理论推导、电路仿真和分析,证明本文提出的电流极限可调状态机可以应用于对负载的检测,通过八个离散量来描述负载情况。负载不同时,功率MOSFET的导通时间可以由电流极限值调节,相对单一的PFM增加了PWM的作用。本状态机用数值电路将数值量转换为模拟量,相对模拟电路增加了电路运行的可靠性和精确度,通过负载反馈来调节电流极限值体现了自适应性。通过验证可行,可以推广应用。

作者简介:

卢治平 男 1975年出生,电子科技大学2000级微电子与固体电子专业二年级研究生,主要从事集成电路设计方面的研究。

参考文献:

[1] “TNY264/266-268” Handbook of Power Integrations 2001

[2] 'Angelo,Kevin P.“Current-limited switch with fast transient response”,U. S. Patent 6,320,365

[3] ross,David A. “Transient over voltage protection circuit for electrical power converters”,U. S. Patent 5,615,097

[4] uzuki,Tadao。“Surge current protection circuit”,U. S. Patent 4,091,434

[5] Schmidt,Thomas A。“Reducing the natural current limit in a power MOS device by reducing the gate-source voltage”, U. S. Patent 5,541,799

[6] Wrathall,Robert S。“Current sense circuit having multiple pilot and reference transistors”,U. S. Patent 5,867,014

[7] 王巍 高德远 有限状态机设计策略 计算机工程与应用 1999(7)

[8] 张溯 胡永华 高明伦 状态机与多时钟体系结构的异同 微电子学与计算机 2001(3)