0 引言

随着系统集成技术(SOC)的飞速发展,基准电压源已成为大规模、超大规模集成电路和几乎所有数字模拟系统中不可缺少的基本电路模块。基准电压源是超大规模集成电路和电子系统的重要组成部分,可广泛应用于高精度比较器、A/D和D/A转换器、随机动态存储器、闪存以及系统集成芯片中。事实上,高性能基准电压源直接影响着电子系统的性能和精度。由于带隙基准电压源能实现高电源抑制比(PSRR)和低温度系数,为此,本文提出了一种基于0.35μm标准CMOS工艺的高性能带隙基准电压源的设计方法。

1 带隙基准电压源的电路设计

1.1 基本原理

本设计利用晶体管基射结电压差△VBE的正温漂去补偿晶体管基射结电压VBE的负温漂,从而实现零温漂。对于恒流源供电的晶体管,其基射结电压VBE随温度的升高而减小。但是,制作在一块集成电路上的两个同类晶体管,如果两者的恒流密度比值不等于1,那么,它们的VBE之差△VBE随温度升高而增大。这样,将上述的VBE和△VBE相加就能实现温度补偿。理论上,当这个相加的电压之和等于硅半导体材料的带隙电压(或外推电压)时,其温度系数为零,这也就是带隙基准电压名称的来历。因为它不使用工作在击穿状态下的齐纳稳压管,所以其噪声电压很低。同时,由于VBE受电源电压变化的影响很小,因此,带隙基准电压源受电源电压变化的影响很小,这就使它具备了高稳定度、低温漂、低噪声的主要优点。事实上,虽然传统带隙基准源结构能输出比较精确的电压,但其电源电压较高(大于3 V),且基准电压范围有限,所以有待改进和提高。

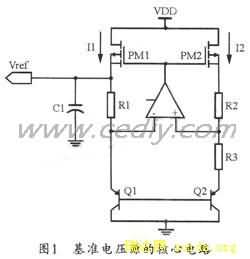

1.2 核心基准电路的设计

根据典型带隙基准电压源的电路结构,考虑到与CMOS工艺的兼容性,设计上可以用PNP晶体管代替NPN晶体管来实现典型带隙基准电压源电路。为了保证两个晶体管的偏置电流具有相同的温度特性,本设计采用PMOS电流源而不是电阻来给晶体管提供偏置电流。

对于n阱CMOS工艺,该基准源的核心电路如R1可提供一个PTAT电流Il,假设双极型晶体管的基射结电压为VBE,则Rl上的电压为:

|

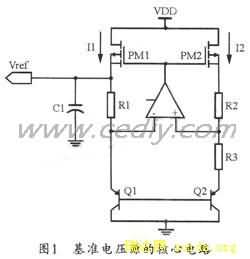

运算放大器是带隙电压基准源电路中的关键之一,其开环增益和输出失调决定了带隙基准源输出的精度和稳定性,VOS的大小可能导致相当大的基准源输出电压误差。此外,VOS自身也是温度的函数。和理想运算放大器相比,该放大电路也会引入一定的误差。这样,为了减小失调对基准电压的影响,运放的失调就要尽可能地小。然而,引起失调的原因很多(如电阻之间的不匹配、晶体管之间的不匹配、运放输入级管子阈值电压的不匹配、运放的有限增益等等)。因此,这里采用常见的两极运算放大器结构,其电路如图2所示。其中,第一级放大是由PM3和PM4两个PMOS作为驱动管,NM1和NM2作为PM3、PM4的有源负载,PM5与PM6、PM7与PM8构成电流镜。第二级放大则由PM6和NM4构成共源放大器,NM4作为驱动管,PM6作为NM4的有源负载,同时也起到镜像电流的作用。它能将第一级差分放大器的单输出信号进一步放大,以得到较高的电压增益。为了能使放大器工作在低压条件下,本设计采用PMOS管作为差分输入级,这样可以降低输入共模电平。而作为输入级的晶体管PM3和PM4,则要求有比较大的栅面积以及最小的栅长,以降低运放的失调电压。此外,运放还可以采用RC补偿网络来获得足够的相位裕度。

|

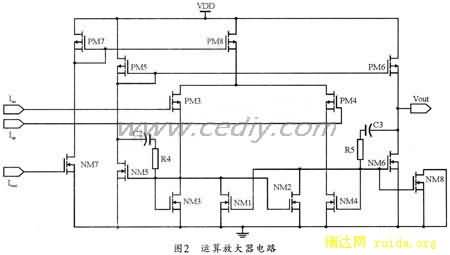

为了提高运算放大器在不同电压和不同温度下的稳定性,以便得到性能较好的带隙基准源,本设计将电流源电路运用于运算放大器中。通过电流源电流可以为参考电压生成电路及电压比较器提供较稳定的偏置电流。理想情况下,该电流与电源电压无关(即偏置电流不随电源电压变化)。该电流源的电路形式如图3所示。

|

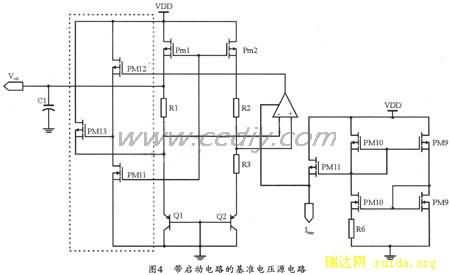

本设计中的启动电路由3个MOS管构成,图4所示是带有启动电路的基准电压源电路,而其启动电路如图4中的左半部分所示。其中PM l2和NM 11构成反相器,PM l3构成共源放大器。由于电路上电时,基准产生电路的所有晶体管均传输零电流,PM 13关断,PM 12的栅极为高电平,因此,经过反相器,PM 13的栅极输入低电平,以使PM 13导通,从而提高PM l3的漏电压,然后使运算放大器输出低电平,进而使整个电路都导通。之后,反相器输入端电压再下降到低电平,输出端变为高电平,从而关断PM 13,以完成整个电路的启动过程,使电路进入正常工作状态。

|

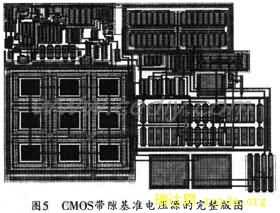

本电路采用0.35μm CMOS标准工艺,设计采用全定制的版图设计,同时,模拟系统在版图设计中采取了许多防范措施,可把串扰、失配、噪音等影响降到最小。版图设计主要使用Cadence公司的VirtuoSo版图设计软件,并用Cadence软件进行电路和版图仿真,最后得到的版图面积为l20 μm×146μm,其完整版图见图5所示。

|

版图完成之后,可以通过提取寄生参数来对电路进行仿真,从而得到温度和电压稳定性曲线。仿真结果显示,两种仿真结果的曲线几乎完全重合,说明本文中的版图设计比较合理,具有较好的实用性。

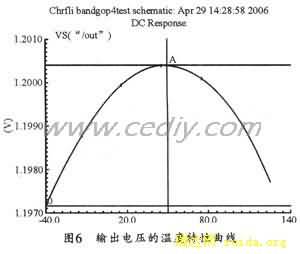

2.2 电路的温度特性

图6所示是本设计的输出电压温度特性曲线。从图6可以看出,当输出基准电压为1.2 V,温度由-40℃变化至125℃时,输出电压变化的绝对值不超过3.2 mV。即电路能够在相当宽的温度变化范围内,保持较高的温度稳定性,其相对温度系数为16 ppm/℃,基本上可以达到最初设定的电路温漂的设计目标(15 ppm/℃)。

|

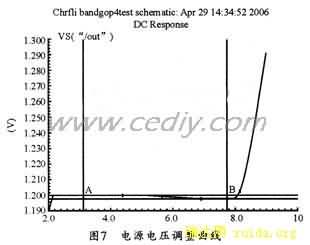

图7所示是本设计的电源电压调整曲线,从图7中可以看出,当输出基准 电压为

1.2 V,而且电源电压由3 V变化至8 V时,其输出电压的绝对值不超过2.21 mV,因而可以看出,其结果基本可以达到设计目标(2.2 mV)。说明电路能够在较宽的电源电压变化范围内,保持较高的电压稳定性。

|

本文从改进电路结构和版图结构的角度来降低失调电压的影响,从而获得了较高的温度精确度,因而具有较高的实用价值。同时,本设计还有电路结构简单,启动性能好,电压输出灵活,工作电压范围宽等特点。通过Cadence中的spectre仿真结果表明,该电路能够满足数字模拟集成电路的要求。