1 引 言

现代频半合成源对频率精度、分辨率、转换时间和频谱纯度等指标提出了越来越高的要求。甚高频(VHF)频率合成器通常采用多锁相环路(PLL)结构,多环合成器将单环中的巨大分频比用多个环路来负担,同时各环,尤其足主环的鉴相频率大幅度提高,从而满足了鉴相频率高、分频比小和分辨率高等要求。但是由于多环组合的固有特性,尤其是分辨率每提高1个数量级,就要增加一级子环路,使得其频率转换速度低、线路复杂、可靠性差。

直接数字式频率合成技术(DDS)的频率分辨率高、频率转换速度快。DDS/PLL混合频率合成是一项新兴技术。DDS激励PLL倍频的方式能发挥DDS高分辨率的特点,但DDS信号中的相噪与杂散一旦落入环路内将会恶化lg N。

采用DDS内插PLL混频,即DDS输出与PLL反馈回路中的压控振荡器(VCO)输出混频,相当于用DDS取代多环频率台成器中的低(细)频率子环,电路结构简单,在频率转换速度、分辨率等方面性能优良,并且不存在DDS相噪与杂散恶化的问题。本文提出基于该思想的一种VHF段频率合成器设计。

2 方案设计

本方案设计一个VHF段频率合成器,输出信号频率分辨高,相位噪声低。

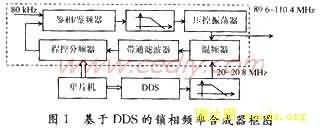

图1所示为频率合成器的原理框图。该合成器原理如下:压控振荡器(VCO)产生VHF段频率信号,在反馈通道中与直接数字式频率合成器(DDS)输出下混频,经带通滤波、程控分频器后送鉴相/鉴频器,与鉴相频率比较得到的相位误差信号,经低通环路滤波后,其平均值控制VCO输出向设定频率值靠拢并最终锁定。

|

本方案采用了DDS取代多环频率合成器中的低(细)频率子环,VCO输出频率范围89.6~110.4 MHz,DDS输出频率范围20~20.8 MHz,混频后取下变频69.6~89.6 MHz,经ECL预置分频器10分频至6.96~8.96 MHz,锁相环(PLL)鉴相频率取80 kHz,内部程控分频范围87~112 kHz。

压控振荡器输出频率和其他信号之间的关系由式(1)给出:

fOUT=N×10×fr+fDDS (1)

其中,fOUT为压控振荡器输出频率,fr为鉴相频率,fDDS为直接频率合成器输出频率,N为内部程控分频比。

3 电路设计

根据图1所示方案,设计了频率合成器的具体电路,其电路框图如图2所示。

|

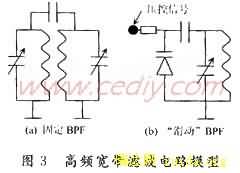

采用DDS内插式混频关键是处理好高频带通滤波环节。可以采用耦合的LC双谐振电路构成69.6~89.6 MHz的固定带通滤波器(BPF),如同3(a)所示,但实际调试发现滤波电路的谐振曲线在20 MHz带宽内很难保持水平。

压控振荡器MC1648采用外接LC电路形式,随压控信号输出89.6~110.4 MHz之间的频率,实际上是外接LC电路的谐振点(可变电容)随压控信号变化,而滤波范围为69.6~89.6 MHz,采用相同的LC电路形式,如图3(b)所示,用VCO的电压榨制信号,改变滤波LC谐振电路的容值,使其谐振频率点与VCO的输出频率“同步”,即滤波谐振频率总是与VCO的输出频率相差约20 MHz左右,称之为“滑动”LC谐振带通滤波电路,考虑到混频后两个边频最少相距20 MHz,可适当降低谐振电路Q值(并联合适电阻),达到69.6~89.6 MHz覆盖,从而灵活解决了高频带通滤波问题。

|

4 主要性能指标分析

4.1 相位噪声

4.1.1 DDS相位噪声

DDS实际上是一个数字分频系统,理论上输出相噪应该以分频比N=fCLK/fDDS相对于系统时钟相噪优化-lg N(dB),0

LDDS=LS-20lg N+δ (2)

其中,LDDS为DDS输出的相噪,LS为参考时钟的相噪,δ为DDS相噪恶化因子。

本方案取fCLK=100 MHz,fDDS=20 MHz,δ=10 dB。可得,DDS相噪相对于参考时钟还改善了4 dB。

4.1.2 锁相环路相位噪声

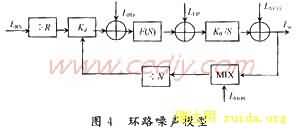

DDS取代多环锁相频率合成器的低频率子环后,环路相位噪声模型如图4所示。

|

根据环路理论,环路总的相噪为:

式中,LRS,LPD,LLP,LVCO,LDDS分别是环路参考晶振、鉴相器、环路滤波器、VCO、DDS的相噪,Lo是系统总输出相噪,H(jω)是环路有效传递函数,为低通滤波因子。

从式(3)可以看出,输出信号近端相位噪声与环路分频比有20lg N的关系,提高主环鉴相频率fr,可减小环路分频比。本方案采用混频方式,在一定程度上也减小了分频比,对带内相位噪声有一定改善。环路带宽外的相噪则主要由VCO的固有噪声决定。

4.2 杂散抑制

直接数字式频率合成(DDS)的相位截断误差,DAC量化误差及DAC非线性等固有特性,导致其输出杂散丰富,如果直接用DDS输山激励锁相倍频,将导致频谱恶化,而本方案采用的内插式混频方式,DDS输出杂散未经锁相倍频,而仍然保持DDS原来输出的水平。在本方案中,按DDS芯片AD9850资料,输出20 MHz时,杂散优于75 dBc。

4.3 频率步进

在本设计中采用ADI的AD9850单片集成直接数字频率合成器,最高时钟允许125 MHz,频率调谐字为32 b。根据DDS的工作原理,其输出频率fo和参考时钟fs,相位累加器长度N以及频率控制字FSW的关系为:

fo=fs×FSW/2N (4)

在100 MHz时钟下工作时,频率分辨率可达23 MHz,完全可满足系统设计的1 Hz频率细调要求。

4.4 跳频时间

跳频时间包含两部分的计算,一部分是DDS跳频时间,另一部分则是环路的频率稳定时间。

DDS核心技术包括相位累加器。正弦表查值,DAC转换及LPF平滑,按芯片AD9850的资料,频率控制寄存器为40 b,采用并行方式需用5个时钟周期(TS)改变频率控制字,FQ_UD信号有效后,间隔tCF输出新的正弦信号。因此DDS跳频时间至少为:

tDDS=5×TS+tCF (5)

当频率变化时,tCF为18个时钟周期(相位变化时为13个时钟周期),这里选择100 MHz时钟,则DDS最怏跳频时间约0.23μs。

锁相环路换频时间是包括可变分频器置数时间、VCO调谐时间和环路捕获时间的总和,VCO的调谐时间可控制在10 μs量级,可变分频器置数可小于100μs。

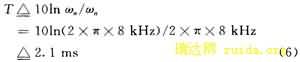

环路捕获时间:

|

4.5 频率范围

如前所述,本方案中合成器输出频率范围89.6~110.4 MHz,DDS输出频率范围20~20.8 MHz,由式(1)可知,粗调频率步进为10×fr=800 kHz,细调频率步进(频率分辨率)为1 Hz,由DDS决定。

5 实验结果

图5所示是合成器输出100 MHz时的频谱图,从图中可以看出,其杂波抑制优于70 dBc,杂波电平优于-50 dBc@10 kHz,噪声电平与RBW平方根成正比,经计算优于:

|

6 结 语

采用DDS取代多环锁相频率合成器的低频率子环,获得了高频率输出(VHF段)、高分辨率(DDS量级)、快转换时间等性能,且结构简单。本方案采用DDS内插PLL混频,而不是DDS直接锁相倍频,避免了 DDS相噪与杂散恶化20lg N的缺点,是DDS,PLL结合的另一种方向,实验证明该方案可行,并且采用本设计方案,应用相应的环路器件及处理方法,可以满足更高的合成频率需要。