1引言

在主PWM控制器位于初级侧的低 DC输出电压隔离型开关电源(SMPS)中,通常采 用专门设计的MOSFET作为同步整流器(SR)。作为 SR使用的MOSFET具有非常小的导通损耗,有助于提 高系统效率。

在初级侧控制的隔离SMPS拓扑中,由 于在隔离变压器次级侧没有PWM控制信号,故欲 产生适当的SR控制信号显得比较困难。但是, 可以从变压器次级输出获得有关数据。由于电 路寄生元件的存在,同步信号在从隔离变压器 输出分离(withdrawn)时,相对于初级PWM信号会发 生延迟,并且在不连续导通模式(DCM)状态会 出现振荡。因此,为SR提供驱动的控制电路必 须能避免发生错误的操作。

在初级侧控制的隔离拓扑中,为驱 动SR需要适当的控制电路,以处理同步时钟信 号(clock)从隔离变压器的输出移开,解决驱动 信号相对于时钟输入的定时 等问题。若对SR控 制不当,在两个器件之间会发生“跨越导通” (crossconduction)。同时,在隔离拓扑的次级由于 相对于初级主开关(MOSFET)驱动信号的延迟, 会在相关元件之间形成短路,发生“贯通”( shootthrough)现象。产生贯通的机理,具体取决于 变换器拓扑结构。

2同步整流器的数字控制方法

在用作产生SR驱动信号的方案 中,首推数字控制方法。

2.1系统基本结构

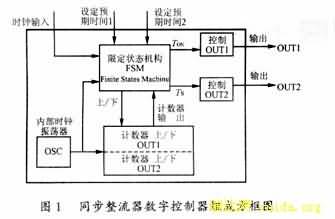

SR数字控制系统一般由振荡器(OSC) 、限定状态机构(FiniteStatesMachine,简写FSM)、两 个耦合的向上/向下(UP/DOWN)计数器和两个控制 输出逻辑等单元电路所组成,系统框图如图1所示。

控制电路有3个输入和2个输出。其 中,2个输出为隔离变换器次级2只MOSFETs提供互补 驱动信号,3个输入包括1个时钟信号和2个输出 的期望(anticipation)时间设定。不论是接通还是 关断,2个输出OUT1和OUT2没有任何交迭。开关频率 为fs的方波信号出现在时钟输入端,期望的定 时通过外部有关输入设定。2个计数器工作方式 及作用不同:DOWN计数器用于处理输出截止,UP计 数器连续获取OUT2开关周期期间或OUT1接通时间内 的有关数据。控制系统根据前面周期内存储的 有关信息,在开关周期截止期内的输出被预先 处理。采用这种控制方法,开关周期和接通时 间(tON)被逐周连续监测。

2.2稳定条件

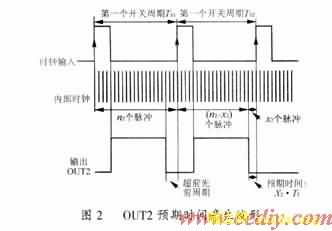

在稳态条件(固定频率和固定占 空比)下,两个开关周期中与输出OUT2相关的波 形如图2所示。

在第1个开关周期(TS1)内, 在时钟输入的上升沿上,两个(UP/DOWN)计数器 中第1个开始计算内部时钟(CK)脉冲。在接下 来的一个时钟输入的上升沿(TS1结束) 上,计数器停止计算。计算过的脉冲数目(n2) 把开关周期的持续时间考虑在内。所存储的数 据,在下一个开关周期中被利用。

在第2个开关周期中,在内部时钟输 入的上升沿上,第1个计数器由大到小计算( countsDOWN)内部时钟脉冲,并且在计算到(n2- x2)个脉冲时终止。第2个计数器计算新 的尚未计算的内部时钟脉冲,并适时修正开关 周期(TS)期间的有关数据。OUT2超前截止总量 为X2·TI(TI为内部时钟脉冲 周期),并通过OUT2预期时间输入设定。计数器 UP或DOWN在每个周期内的功能,相对于先前周期 被交换。

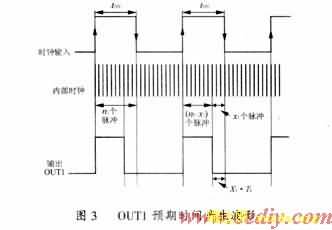

为预期关断OUT1,另外两个UP/DOWN计数 器将考虑计及接通时间(tON)期间的有 关数据,相关波形如图3所示。

在第1个开关周期内,第1个计数器 在时钟输入上升沿上开始计数,并且在时钟输 入下降沿上停止。其间计算的脉冲数量为n1, 只计及tON时间之内的脉冲数。

在第2个开关周期内,第1个计数器递 减计数,在计算到n1-x1时停止。 关断OUT1的超前时间总计为x1·Ti,并 由OUT1预期时间输入设定。第2个计数器向上(由 小到大)计算时钟输入上升沿与下降沿之间的 脉冲数目。

2.3变化条件

2.3.1开关频率发生变化

当开关频率(fs)发生变化时 ,对于输出OUT2而言,可能存在三种情况:

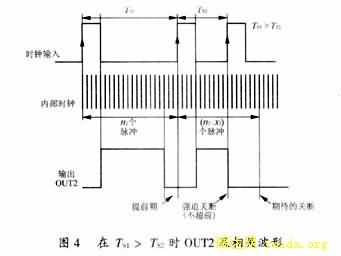

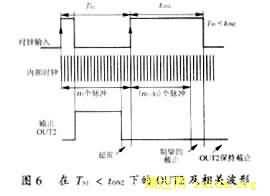

1)TS1>TS2

当第2个开关周期TS2小于先前周期TS1时 ,OUT2的截止发生延迟,相对于时钟输入没有超 前,而是随时钟输入的前沿强迫关断。图4示出 了该条件下的相关波形。

2)TS1>TS2

关波形如图5所示。在此情况下,OUT2发 生提前关断。MOSFET体二极管的导通时间恰为一个周期,效率损失非常小。

3)TS1

2.3.2占空比发生变化

对于输出OUT1,当接通时间tON发 生变化时,可能会出现两种不同的情况:

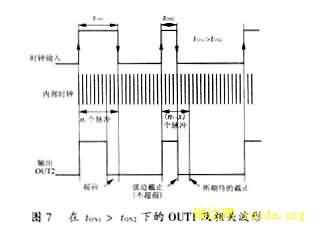

1)tON1>tON2当第1个开关 周期的接通时间tON1大于第2个开关周期的 接通时间tON2时,时钟输入、内部时钟和输出OUT1波 形定时图如图7所示。在此情况下,OUT1的关断被 延时,相对于时钟输入没有提前,总是在时钟 输入的下降沿上即时截止。

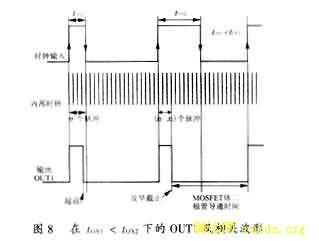

2)tON1上述的方法通过对前一个周期的测量来确定下 一个周期的动作,履行逐周控制。预期关断同 步整流器MOSFET的内部时钟脉冲总数是X1或X2。 内部振荡器频率(fi)越高,预期时间 精度也就越高。

3STSRx系列智能驱动器ICs

STSRx系列IC是ST公司为驱动隔离 SMPS中的同步整流器而专门设计的器件。该系列 ICs的时钟信号从隔离变压器的次级输出获取, 为驱动用作SR的1只或2只MOSFETs,输出适当的控制 信号。

3.1STSR2

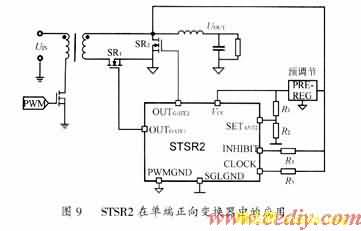

STSR2用作驱动单端正向拓扑中的两 个同步整流器。该IC包含前面所叙述的控制系 统,内置两个大电流N沟道MOSFET驱动器和一个时 钟缓冲器等单元电路。STSR2的引脚名称及其应用 电路如图9所示。

STSR2的引脚功能如下:

VCC电源电压,范围为4.5~5.5V;

PWRGND和SGLGND分别为功率信号和控制逻 辑信号的参考端;

CLOCK同步信号输入;

OUTGATE1/22个大电流互补输出。 由于IC自身产生死区时间,在两个开通时间之 间不存在任何交迭;

SETANT2为OUTGATE2设定预期截止时 间(有4种不同的期望时间可供选择);

INHIBIT当该脚输入高于非常低的一 个门限电压时,OUTGATE2使能。在正向变换器应用 中,迫使OUTGATE2的接通时间减至最小。

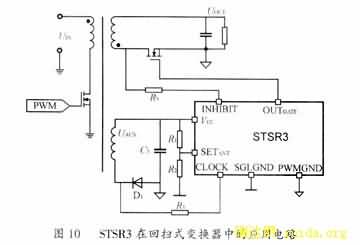

3.2STSR3

STSR3是为驱动在回扫式拓扑中的一 个SR而专门设计的控制IC,其引脚名称(符号) 及应用电路如图10所示。STSR3与STSR2比较,主要区 别是STSR3仅有一个大电流栅极驱动输入(OUTGATE) 。

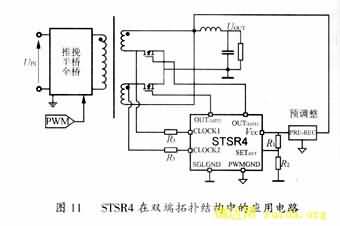

3.3STSR4

STSR4是指定用于驱动推挽、半桥或 全桥式双端输出拓扑结构中SR的控制IC。该器件 的典型应用电路如图11所示。STSR4含有两个大电 流N沟道MOSFETs驱动器输出,同时有两个时钟输入 (CLOCK1和CLOCK2),分别接收来自隔离变压器次级 绕组上的时钟信号。STSR2、STSR3和STSR4在不同类型的隔离式 拓扑结构应用中,都是从变压器的次级输出获 得时钟信号,对作为SR使用的一只或两只MOSFETs产 生恰当的栅极驱动信号,完全解决了在控制SR中 易于出现的全部问题,有效地提高了系统稳定 性和可靠性。

4结语

在隔离SMPS拓扑中,用于驱动SR的 数字控制/驱动技术,相对于需要附加磁复位技 术的所谓“自驱动同步整流”方法来说,具有 许多优点。数字控制方法主PWM控制器在初级侧 的SMPS隔离拓扑中,为利用直接来自于变。